#### SFP-DD MIS

## **Management Interface Specification**

for

## **SFP Double Density 2X Pluggable Transceiver**

#### Revision 2.0

## September 25, 2020

Abstract: This document defines the SFP-DD Management Interface Specification (MIS) that may be used by 2 lane pluggable modules with host to module management communication based on a Two-Wire-Interface (TWI). This document provides a common specification for systems manufacturers, system integrators, and suppliers of modules and transceivers.

#### **POINTS OF CONTACT:**

Ali Ghiasi (Current Technical Editor) Ghiasi Quantum 19947 Lindenbrook Lane Cupertino, CA 95014 ali at ghiasiguantum dot com

Tom Palkert (Prior Technical Editor) tom.palkert at molex dot com

Scott Sommers (Chair)

Molex

2222 Wellington Court

Lisle, IL 60532-1682

scott.sommers at molex dot com

#### Website:

www.sfp-dd.com

#### Limitation on use of Information:

This specification is provided "**AS IS**" with **NO WARRANTIES** whatsoever and therefore the provision of this specification does not include any warranty of merchantability, noninfringement, fitness for a particular purpose, or any other warranty otherwise arising out of any proposal, specification or sample. The authors further disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

#### Permissions:

You are authorized to download, reproduce and distribute this document. All other rights are reserved. The provision of this document should not be construed as the granting of any right to practice, make, use or otherwise develop products that are based on the document. Any and all IP rights related to this document and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the respective owners of those IP rights.

The following are Promoter member companies of the SFP-DD MSA.

| Alibaba Group | Hewlett Packard Enterprise | Lumentum        |

|---------------|----------------------------|-----------------|

| Broadcom      | Huawei                     | Molex           |

| Cisco         | Intel                      | TE Connectivity |

| DellEMC       | Juniper Networks           |                 |

| II-VI         | Nvidia                     |                 |

The following are Contributor member companies of the SFP-DD MSA.

| Accelink                        | Genesis Connected Solutions | Nokia            |  |

|---------------------------------|-----------------------------|------------------|--|

| Amphenol                        | Hisense Broadband           | Senko            |  |

| AOI                             | Infinera                    | Source Photonics |  |

| Eoptolink                       | InnoLight                   | US Conec         |  |

| Foxconn Interconnect Technology | Maxim Integrated            | ZTE              |  |

| Fourte International            | MultiLane                   |                  |  |

**Change History:**

| <u> </u> | shange motory.     |                                                                                                                                                                                                                                                                                                                                        |  |

|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision | Date               | Changes                                                                                                                                                                                                                                                                                                                                |  |

| 1.0      | September 18, 2019 | First public release                                                                                                                                                                                                                                                                                                                   |  |

| 2.0      | September 25, 2020 | Following enhancement are made: stage set ready registers added, fault definition now is inline with SFP and limited to laser eye safety or other hazards, IntL/TxFault dual use operation defined, host electrical lanes limited to 2, power classes now consistent with SFP-DD HW definition, updated SFP-DD vs CMIS signals naming. |  |

|          |                    |                                                                                                                                                                                                                                                                                                                                        |  |

### **Foreword**

The development work on this specification was done by the SFP-DD MSA, an industry group. The membership of the committee since its formation in May 2017 has included a mix of companies which are leaders across the industry.

## **Table of Contents**

| 1 | SC         | SCOPE AND PURPOSE                                                     | 10 |

|---|------------|-----------------------------------------------------------------------|----|

| 2 | RI         | REFERENCES AND CONVENTIONS                                            | 11 |

|   | 2.1        | Industry Documents                                                    | 11 |

|   | 2.2        | Sources                                                               | 11 |

|   | 2.3        | CONVENTIONS                                                           | 11 |

| 3 | KI         | KEYWORDS, ACRONYMS, AND DEFINITIONS                                   | 13 |

|   | 3.1        | Keywords                                                              | 1: |

|   | 3.2        |                                                                       |    |

|   | 3.3        |                                                                       |    |

| 4 |            | NTRODUCTION AND GENERAL DESCRIPTION                                   |    |

|   |            |                                                                       |    |

|   | 4.1<br>4.2 |                                                                       |    |

|   |            |                                                                       |    |

| 5 | M          | MANAGEMENT INTERFACE                                                  | 18 |

|   | 5.1        | Management Control Signals                                            | 18 |

|   | 5.2        |                                                                       |    |

|   | 5.         | 5.2.1 General Description                                             | 18 |

|   | 5.         | 5.2.2 Physical Layer                                                  |    |

|   | 5.3        | SERIAL COMMUNICATION PROTOCOL                                         | 19 |

|   | 5.         | 5.3.1 Basic Definitions                                               | 19 |

|   |            | 5.3.1.1 Start Condition (START)                                       | 19 |

|   |            | 5.3.1.2 Stop Condition (STOP)                                         |    |

|   |            | 5.3.1.3 Word Size (Byte)                                              |    |

|   |            | 5.3.1.4 Basic Operation Encoding (Control Byte)                       |    |

|   |            | 5.3.1.5 Acknowledge (ACK)                                             |    |

|   |            | 5.3.1.7 Acknowledge Polling                                           |    |

|   | 5.         | 5.3.2 Protocol Reset and Recovery                                     |    |

|   |            | 5.3.2.1 Power On Reset                                                |    |

|   |            | 5.3.2.2 Protocol Reset and Recovery                                   |    |

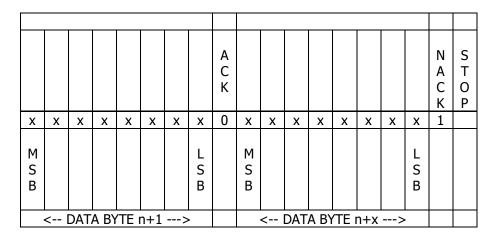

|   | 5.         | 5.3.3 Binary Serial Frame Format for Basic Operations                 | 20 |

|   |            | 5.3.3.1 Read/Write Control Byte and Response                          |    |

|   |            | 5.3.3.2 Byte Address and Data                                         |    |

|   | 5.4        | ,                                                                     |    |

|   |            | Slave Memory Current Byte Address Counter (Read and Write Operations) |    |

|   | _          | 5.4.2 Data Coherency                                                  |    |

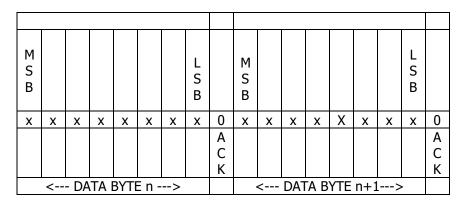

|   | 5.         | 5.4.3 Byte Read Operations                                            |    |

|   |            | 5.4.3.1 Current Address Read Operation                                |    |

|   | 5          | 5.4.4 Sequential Bytes Read Operation                                 |    |

|   | ٥.         | 5.4.4.1 Sequential Read from Current Start Address                    |    |

|   |            | 5.4.4.2 Sequential Read from Random Start Address                     |    |

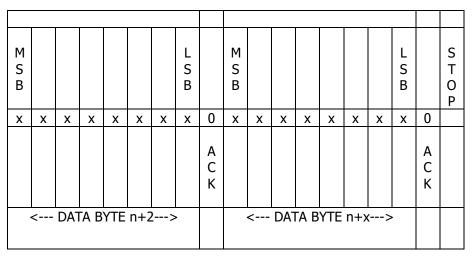

|   | 5.         | 5.4.5 Byte Write Operation                                            |    |

|   | 5.         | 5.4.6 Sequential Bytes Write Operation                                |    |

|   | 5.5        |                                                                       |    |

| 6 | C          | CORE MANAGEMENT FEATURES                                              | 29 |

|   | 6.1        | Module Management Basics                                              |    |

|   | -          | 5.1.1 Host Interface Conventions                                      |    |

|   | _          | 5.1.2 Media Interface Conventions                                     |    |

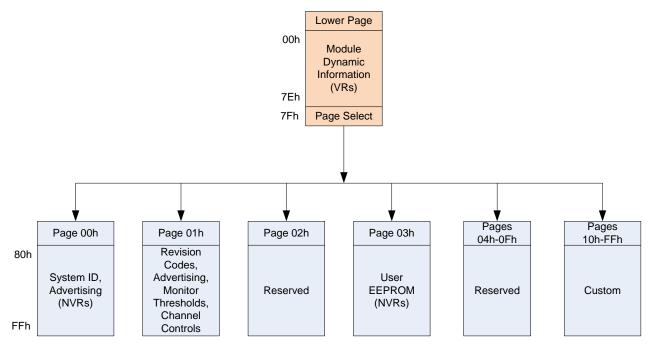

|   | _          | 5.1.3 Interface Memory Map Representations                            |    |

|   |            |                                                                       |    |

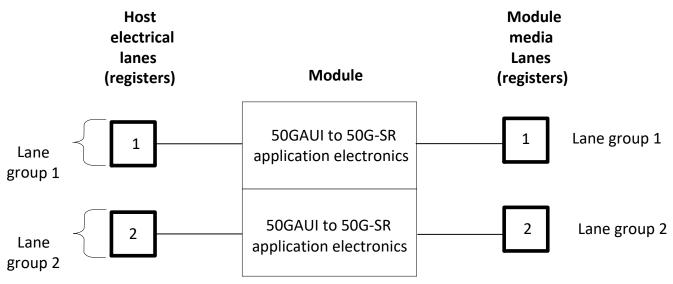

| 6.2 Mo             | DDULE FUNCTIONAL MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.2.1              | Functional Module Capabilities – Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 6.2.1.             | 1 Advertising Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

| 6.2.2              | Logical Module Use – Data Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

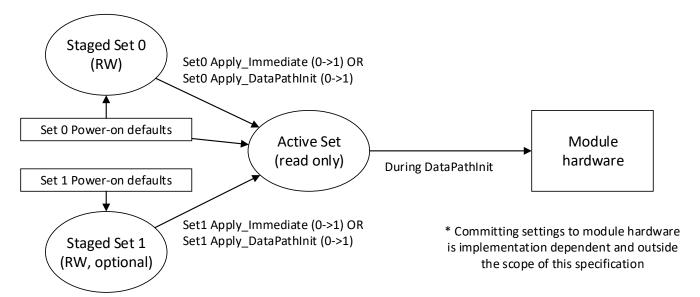

| 6.2.3              | Data Path Configuration — Control Sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33 |

| 6.2.3.             | 1 Control Set Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

| 6.2.3.             | and the state of t |    |

| 6.2.4              | Signal Integrity Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 6.2.4.             | Free days are as a second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 6.2.4.             | The state of the s |    |

| 6.2.4.             | the state of the s |    |

| 6.2.4.4            | 1 1 1 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

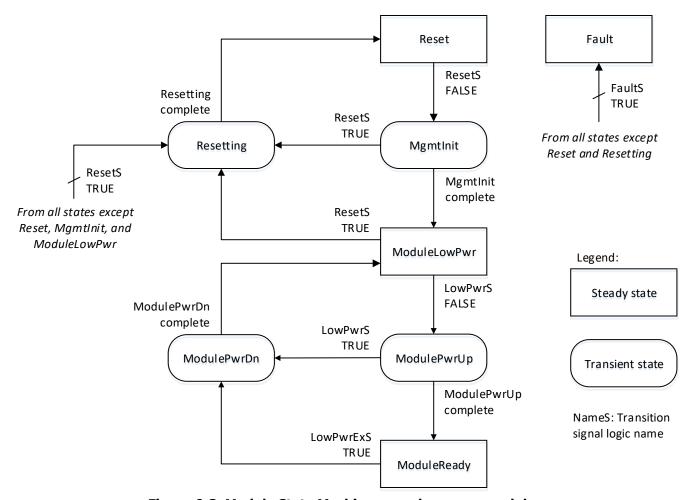

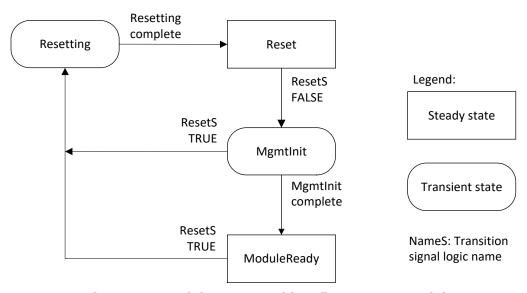

|                    | DDULE BEHAVIORAL MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 6.3.1              | Module State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 6.3.1.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.1.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.1.4<br>6.3.1.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.1.             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 6.3.1.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.1.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.1.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.1.9            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 6.3.1.             | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 6.3.1.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

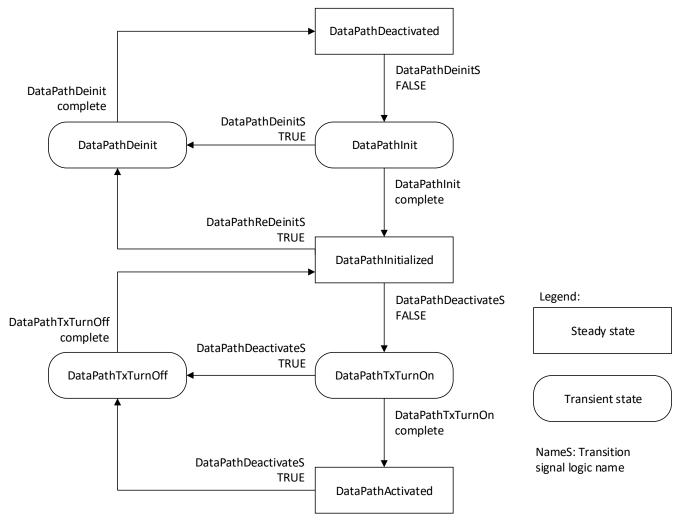

| 6.3.2              | Data Path State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48 |

| 6.3.2.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.2.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 6.3.2.3            | 3 DataPathInit State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

| 6.3.2.4            | 4 DataPathInitialized State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55 |

| 6.3.2.             | 5 DataPathDeinit State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 |

| 6.3.2.             | 6 DataPathTxTurnOn State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56 |

| 6.3.2.             | 7 DataPathActivated State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

| 6.3.2.             | B DataPathTxTurnOff State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

| 6.3.3              | Interrupt Flag Conformance per State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58 |

| 6.3.3.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |