43

44

#### **QSFP-DD MSA**

#### QSFP-DD/QSFP-DD800/QSFP112 Hardware Specification

for

#### **QSFP DOUBLE DENSITY 8X AND QSFP 4X PLUGGABLE TRANSCEIVERS**

**Revision 6.3**

July 26, 2022

Abstract: This specification defines: the electrical and optical connectors, electrical signals and power supplies, mechanical and thermal requirements of the pluggable QSFP Double Density (QSFP-DD/QSFP-DD800) and the QSFP112 module in the classic 4-lanes QSFP form factor, connector and cage system. This document provides a common specification for systems manufacturers, system integrators, and suppliers of modules.

#### POINTS OF CONTACT:

Ali Ghiasi (Technical Editor) Ghiasi Quantum 19947 Lindenbrook Lane Cupertino, CA 95014 ali at ghiasiquantum dot com

Mark Nowell (Co-Chair) Cisco 170 West Tasman Dr San Jose, CA 95134 mnowell at cisco dot com Scott Sommers (Co-Chair) Molex 2222 Wellington Court Lisle. IL 60532-1682 scott.sommers at molex dot com

#### Website:

www.QSFP-DD.com

#### Limitation on use of Information:

This specification is provided "AS IS" with NO WARRANTIES whatsoever and therefore the provision of this specification does not include any warranty of merchantability, noninfringement, fitness for a particular purpose, or any other warranty otherwise arising out of any proposal, specification or sample. The authors further disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

#### **Permissions:**

You are authorized to download, reproduce and distribute this document. All other rights are reserved. The provision of this document should not be construed as the granting of any right to practice, make, use or otherwise develop products that are based on the document. Any and all IP rights related to this document and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the respective owners of those IP rights.

# Dedication:The memberan excellent

5

The members of the QSFP-DD MSA would like to acknowledge the contributions of Mr. Edmund Poh. He was an excellent engineer; his technical skills and collaborative attitude will be missed.

The following are Promoter member companies of the QSFP-DD MSA.

| Broadcom | Foxconn Interconnect Technology | Lumentum        |

|----------|---------------------------------|-----------------|

| Cisco    | Huawei                          | Nvidia          |

| Corning  | Intel                           | Molex           |

| II-VI    | Juniper Networks                | TE Connectivity |

The following are contributing member companies of the QSFP-DD MSA.

| ACON                        | H3C                        | Panduit               |

|-----------------------------|----------------------------|-----------------------|

| Alibaba Group               | Hisense Broadband          | PHY-SI                |

| Amphenol                    | Hitachi Metals             | Ranovus               |

| Applied Optoelectronics     | Hewlett Packard Enterprise | Samtec                |

| Apresia                     | Infinera                   | Semtech               |

| Celestica                   | InnoLight                  | Senko                 |

| Ciena                       | JPC                        | Sicoya                |

| CIG                         | Keysight Technologies      | The Siemon Company    |

| ColorChip                   | Leoni                      | Skorpios              |

| Credo                       | Lorom Cable Connection     | Source Photonics      |

| Dell Technologies           | Luxshare ICT               | Spectra7 Microsystems |

| Delta Products              | Macom                      | Spirent               |

| Dust Photonics              | Marvell                    | Sumitomo Electric     |

| Eoptolink                   | MaxLinear                  | US Conec              |

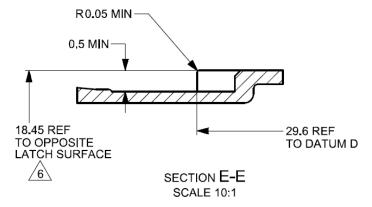

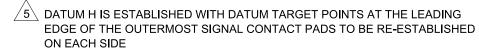

| Fourte                      | MultiLane                  | Xilinx                |

| Fujitsu Optical Components  | NEC Corporation            | Yamaichi              |

| Genesis Connected Solutions | Nokia                      |                       |

**Change History:**

| Revision | Date           | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | Sept 19, 2016  | First public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.0      | March 13, 2017 | Second public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.0      | Sept 19, 2017  | Third public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.0      | Sept 18, 2018  | Fourth public release, Additions of thermal chapter 10, synchronous clocking in 4.9, Mechanical updates.                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.0      | July 9, 2019   | Fifth public release, Added Module type 2A, changes to latch and cage drawings, added ePPS contact, updated power supply testing, added BiDi optical port assignments.                                                                                                                                                                                                                                                                                                                             |

| 5.1      | August 7, 2020 | 6 <sup>th</sup> public release, Chapter 7-Management Interface is now part of Chapter 4. Port mapping, optical connectors, and module color coding moved into a new Chapter 6.                                                                                                                                                                                                                                                                                                                     |

| 6.0      | May 20, 2021   | 7 <sup>th</sup> public release, chapters for QSFP-DD800 and QSFP112 Mechanical and Board Definitions are added. Chapter for QSFP112 Electrical and management timing added. Updated power supply test method. Module power contacts rating increased from 1 A to 1.5 A and max module power dissipation increased to at least 25 W. Programmable/Vendor specifics and ePPS/Clock contacts defined. Normative connector performance Appendix A added.                                               |

| 6.01     | May 28, 2021   | 8 <sup>th</sup> public release, reinstated text inadvertently deleted in PCB notes in section 7.3 and 8.3, inadvertent change to a dimension in Figure 55 corrected.                                                                                                                                                                                                                                                                                                                               |

| 6.2      | March 11, 2022 | 9 <sup>th</sup> public release, defined a new improved power supply test method, squelch level reduced to 50 mV for 112G operation, press hole separation increased to 3.1 mm in Figure 78, corner radius added to Figure 88. TWI bus timing removed from chapter 4 as identical timing diagram already included in CMIS. QSFP112 specification has been forwarded to the SNIA TA TWG and chapter 5 and 9 are not being updated and will be removed when SNIA TA specification has been published. |

| 6.3      | July 26, 2022  | 10 <sup>th</sup> public release, updated termination definition for P/VSx and ePPS/Clock signals, Figure 61 bezel opening height adjusted for consistency, updated Figure 85 glue zone, and updated Figure 95 to further clarify blocking features.                                                                                                                                                                                                                                                |

#### Foreword

The development work on this specification was done by the QSFP-DD MSA, an industry group. The membership of the committee since its formation on Feb 2016 has included a mix of companies which are leaders across the industry.

|   |                | TABLE of CONTENTS                                                        |    |

|---|----------------|--------------------------------------------------------------------------|----|

| 1 | SCO            | PE                                                                       | 10 |

| - |                | DESCRIPTION OF CHAPTERS                                                  |    |

| 2 |                | RENCES AND ACRONYMS                                                      |    |

| 2 |                |                                                                          |    |

|   |                | REFERENCE STANDARDS AND SPECIFICATIONS                                   |    |

|   |                | SFF SPECIFICATIONS:                                                      |    |

|   |                | ACRONYMS AND ABBREVIATIONS                                               |    |

| _ |                |                                                                          |    |

| 3 |                | ODUCTION                                                                 |    |

|   |                | DOCUMENT OVERVIEW AND ORGANIZATION                                       |    |

|   |                | APPLICATIONS                                                             |    |

|   | 3.3            | MODULE MANAGEMENT AND CONTROL                                            | 14 |

| 4 | QSFF           | P-DD/QSFP-DD800 ELECTRICAL SPECIFICATION AND MANAGEMENT INTERFACE TIMING | 15 |

|   | 4.1 I          | ELECTRICAL CONNECTOR                                                     | 15 |

|   | 4.2 l          | LOW SPEED ELECTRICAL HARDWARE SIGNALS                                    | 20 |

|   | 4.2.1          | ModSelL                                                                  | 20 |

|   | 4.2.2          | ResetL                                                                   | 20 |

|   | 4.2.3          | LPMode/TxDis                                                             | _  |

|   | 4.2.4          |                                                                          |    |

|   | 4.2.5          | IntL/RxLOSL                                                              |    |

|   | 4.2.6          | Programmable/Vendor Specific (Optional)                                  |    |

|   |                | ePPS/Clock PTP Reference Clock (Optional)                                |    |

|   |                | EXAMPLES OF QSFP-DD/QSFP-DD800 HOST BOARD SCHEMATIC                      |    |

|   |                | TWI Logic Levels and Bus Loading                                         |    |

|   |                | Management Interface                                                     |    |

|   |                | Management Interface Timing Specification                                |    |

|   |                | Timing for soft control and status functions                             |    |

|   |                | HIGH SPEED ELECTRICAL SPECIFICATION                                      |    |

|   | 4.6.1          | Rx(n)(p/n)                                                               | 34 |

|   | 4.6.2          | Tx(n)(p/n)                                                               | 34 |

|   | <i>4.7</i>     | Power Requirements                                                       |    |

|   | 4.7.1          | Power Classes and Maximum Power Consumption                              |    |

|   |                | Host Board Power Supply Filtering                                        |    |

|   | 4.7.3          | Module Power Supply Specification                                        |    |

|   | 4.7.4          |                                                                          |    |

|   | 4.7.5<br>4.7.6 | Module Power Supply Noise Output                                         |    |

|   | _              | SD                                                                       |    |

|   |                | CLOCKING CONSIDERATIONS                                                  |    |

|   | 4.9.1          | Data Path Description                                                    |    |

|   | 4.9.2          | TX Clocking Considerations                                               |    |

|   | 4.9.3          |                                                                          |    |

| 5 | QSFF           | P112 ELECTRICAL SPECIFICATION AND MANAGEMENT INTERFACE TIMING            | 43 |

|   | 5.1 (          | QSFP112 ELECTRICAL CONNECTOR                                             | 43 |

|   |                | QSFP112 Low Speed Electrical Hardware Signals                            |    |

|   |                | ModSelL                                                                  |    |

|   | 5.2.2          | ResetL                                                                   | 46 |

| 1  | 5.2.3 LPMode/TxDis                                             | 46  |

|----|----------------------------------------------------------------|-----|

| 2  | 5.2.4 ModPrsL                                                  | 47  |

| 3  | 5.2.5 IntL/RxLOSL                                              | 47  |

| 4  | 5.3 EXAMPLES OF QSFP112 HOST BOARD SCHEMATIC                   | 47  |

| 5  | 5.4 LOW SPEED ELECTRICAL SPECIFICATION                         | 51  |

| 6  | 5.4.1 TWI Logic Levels and Bus Loading                         | 51  |

| 7  | 5.5 Management Interface                                       | 52  |

| 8  | 5.5.1 Management Interface Timing Specification                | 53  |

| 9  | 5.5.2 Timing for soft control and status functions             | 58  |

| 10 | 5.6 HIGH SPEED ELECTRICAL SPECIFICATION                        | 60  |

| 11 | 5.6.1 Rx(n)(p/n)                                               | 60  |

| 12 | 5.6.2 Tx(n)(p/n)                                               |     |

| 13 | 5.7 POWER REQUIREMENTS                                         | 61  |

| 14 | 5.7.1 QSFP112 Power Classes and Maximum Power Consumption      | 61  |

| 15 | 5.7.2 QSFP112 Host Board Power Supply Filtering                |     |

| 16 | 5.7.3 Module Power Supply Specification                        |     |

| 17 | 5.7.4 Host Board Power Supply Noise Output                     |     |

| 18 | 5.7.5 Module Power Supply Noise Output                         |     |

| 19 | 5.7.6 Module Power Supply Noise Tolerance                      |     |

| 20 | 5.8 ESD                                                        |     |

| 21 | 5.9 CLOCKING CONSIDERATIONS                                    |     |

| 22 | 5.9.1 Data Path Description                                    |     |

| 23 | 5.9.2 TX Clocking Considerations                               |     |

| 24 | 5.9.3 Rx Clocking Considerations                               |     |

| 25 | 6 OPTICAL PORT MAPPING AND OPTICAL INTERFACES                  |     |

| 25 |                                                                |     |

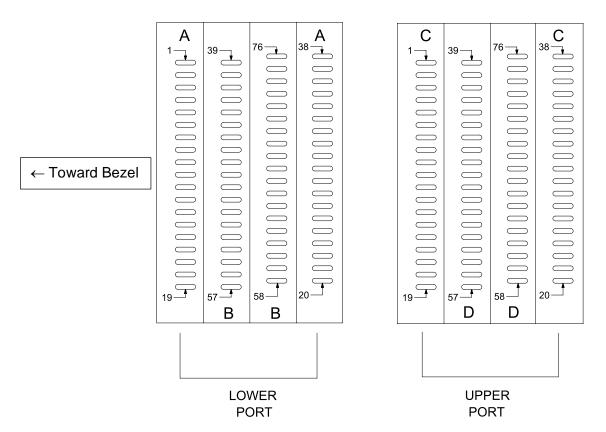

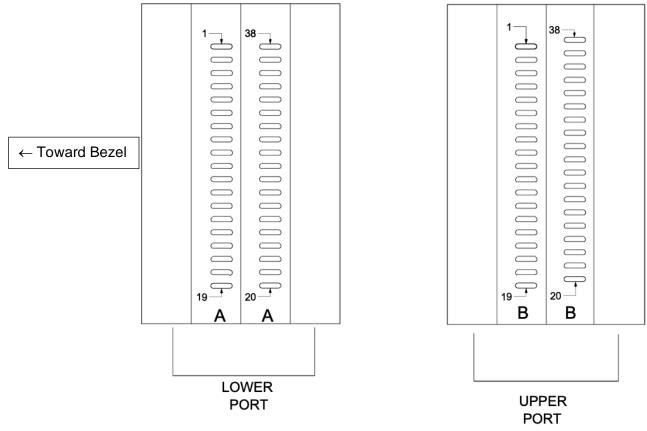

| 26 | 6.1 ELECTRICAL DATA INPUT/OUTPUT TO OPTICAL PORT MAPPING       | 68  |

| 27 | 6.2 OPTICAL INTERFACES                                         | 68  |

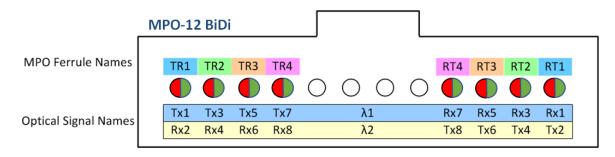

| 28 | 6.2.1 MPO Optical Cable connections                            | 71  |

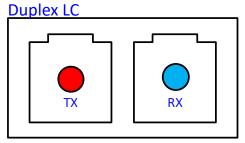

| 29 | 6.2.2 Duplex LC Optical Cable connection                       | 74  |

| 30 | 6.2.3 Dual CS Optical Cable connection                         | 74  |

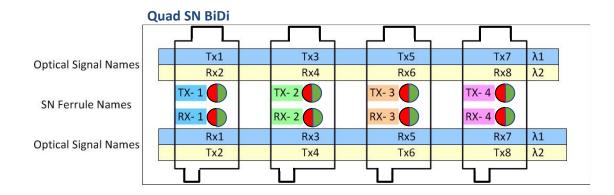

| 31 | 6.2.4 Quad SN Optical Cable connections                        | 75  |

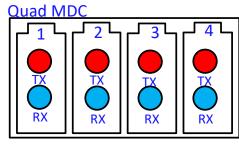

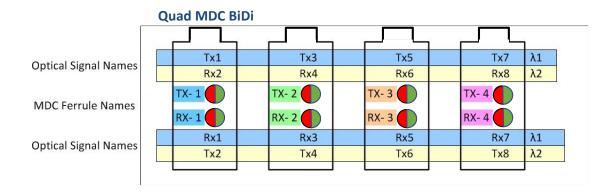

| 32 | 6.2.5 Quad MDC Optical Cable connection                        | 75  |

| 33 | 6.2.6 Dual SN Optical Cable connections                        | 76  |

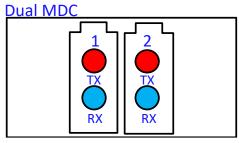

| 34 | 6.2.7 Dual MDC Optical Cable connection                        |     |

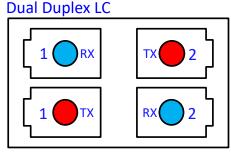

| 35 | 6.2.8 Dual Duplex LC Optical Cable connection                  | 77  |

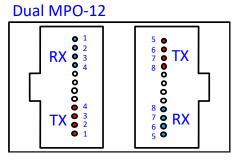

| 36 | 6.2.9 Dual MPO-12 Optical Cable connection                     | 78  |

| 37 | 6.3 MODULE COLOR CODING AND LABELING                           | 79  |

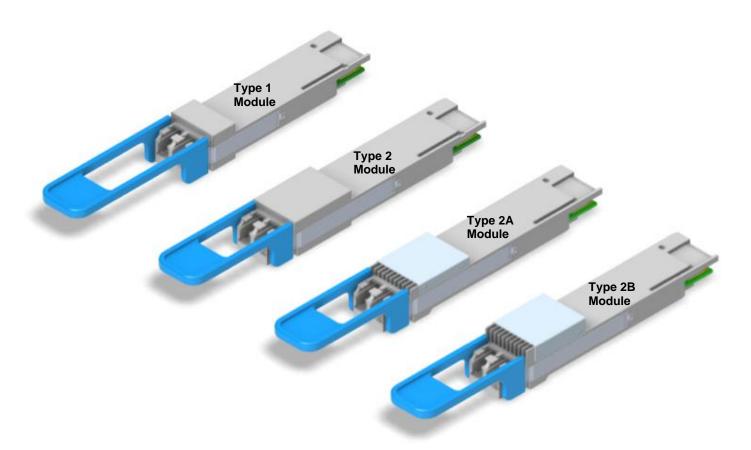

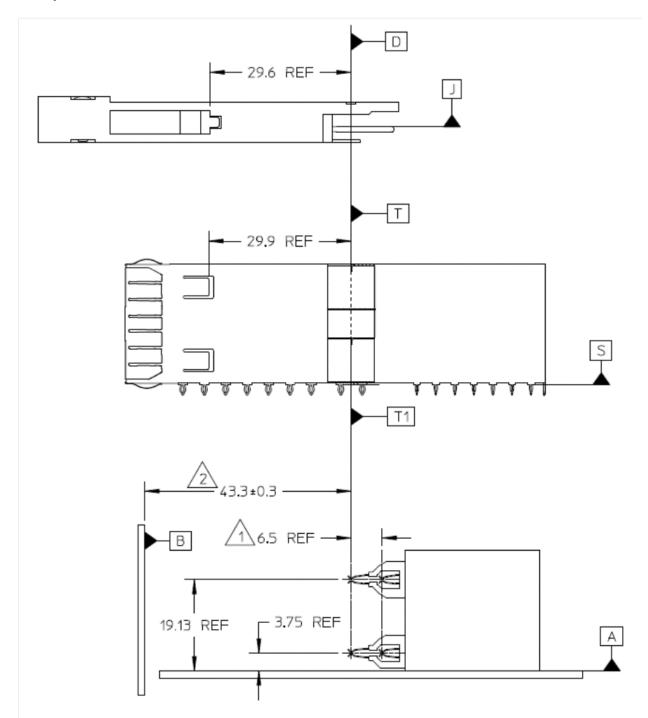

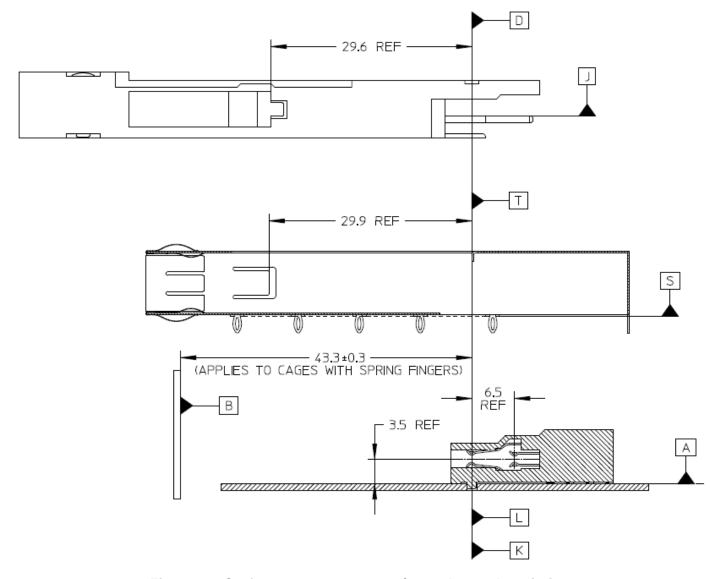

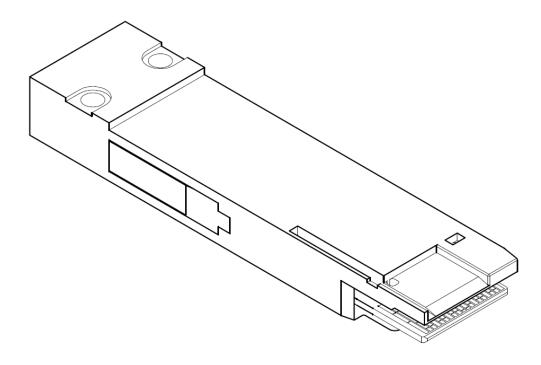

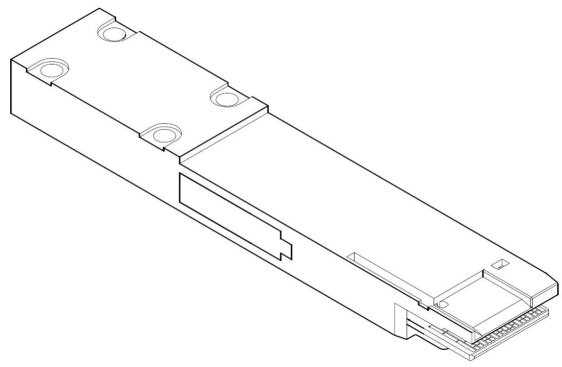

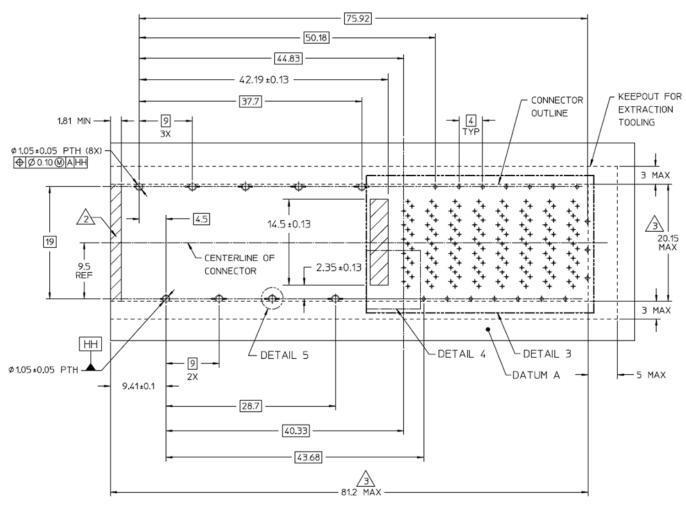

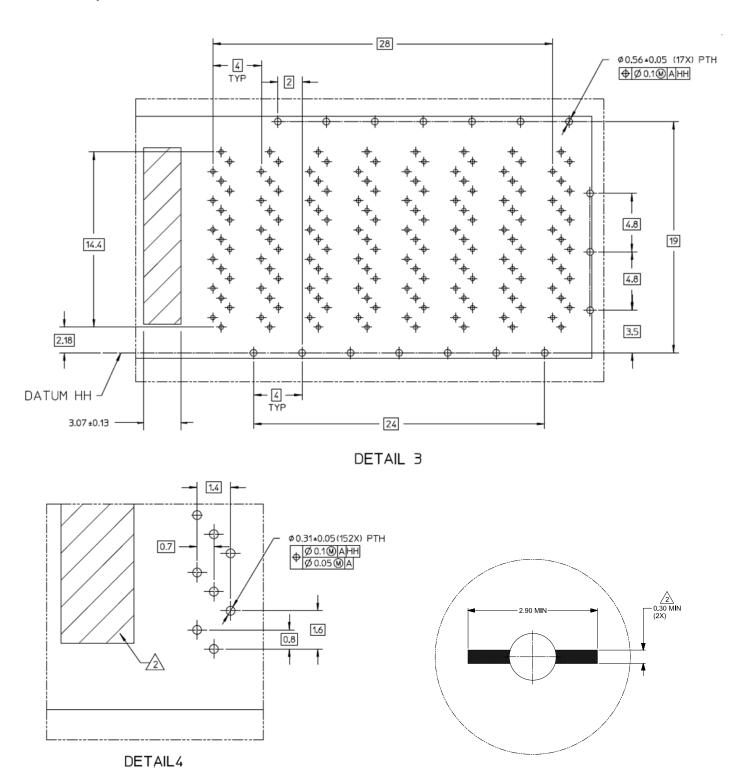

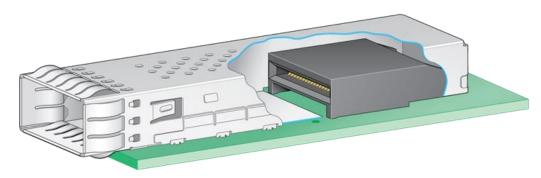

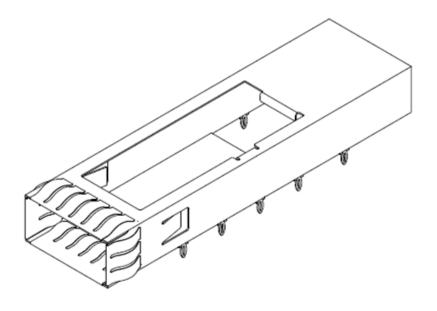

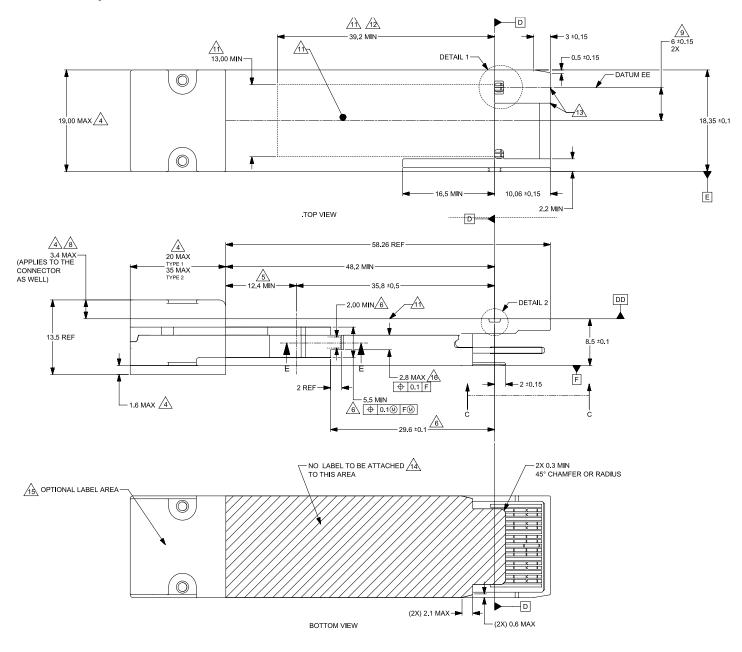

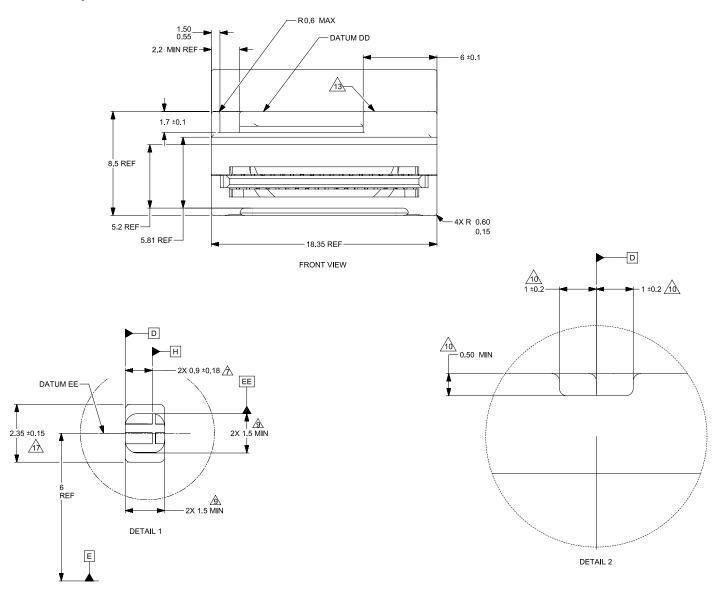

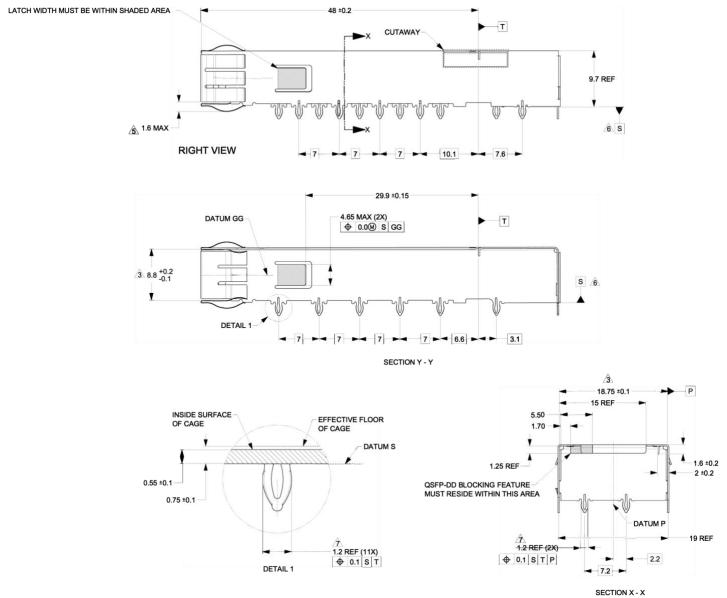

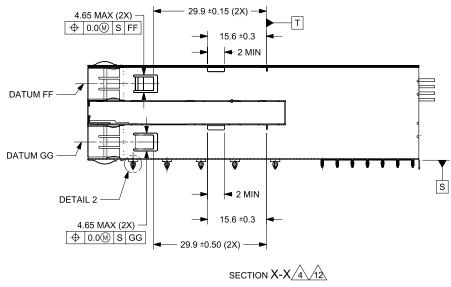

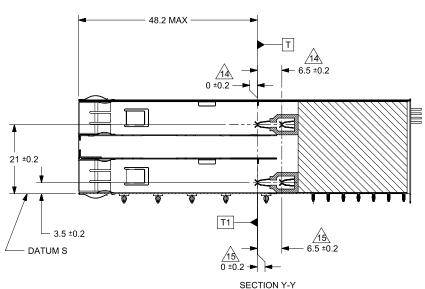

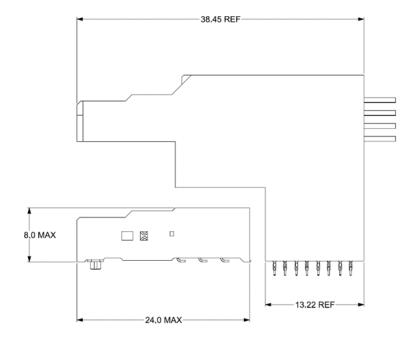

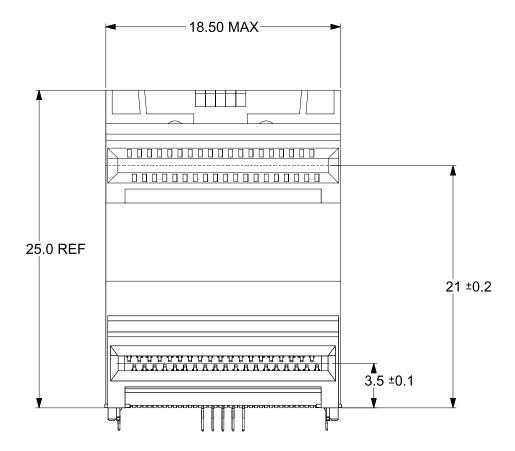

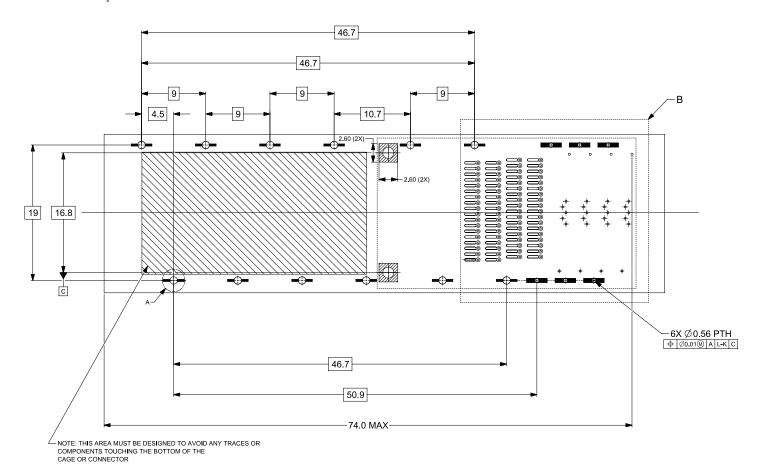

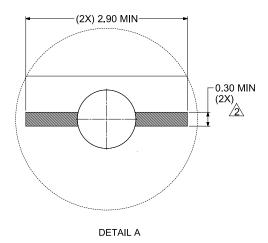

| 38 | 7 QSFP-DD MECHANICAL AND BOARD DEFINITION                      | 80  |

|    |                                                                |     |

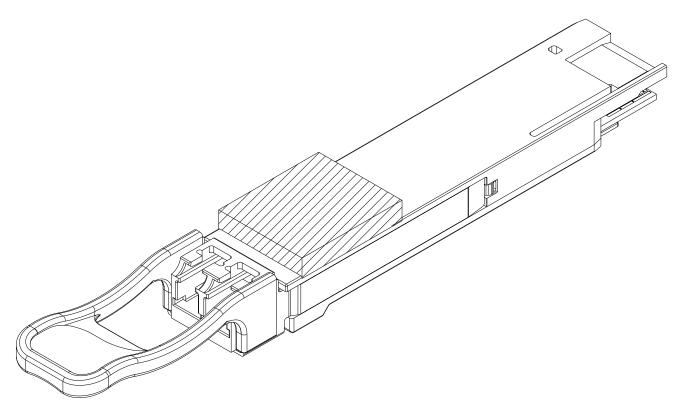

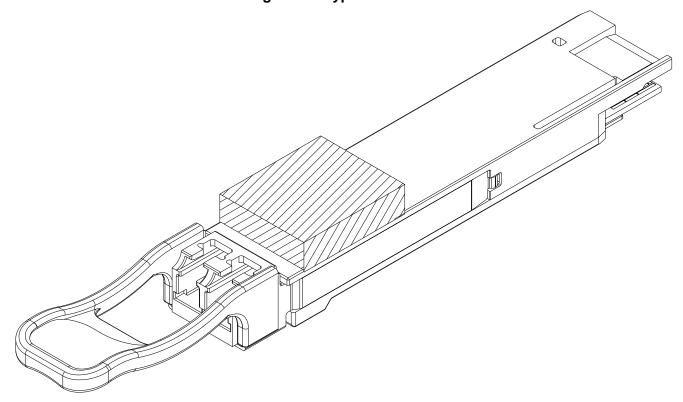

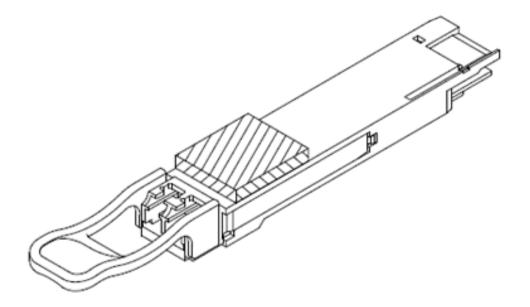

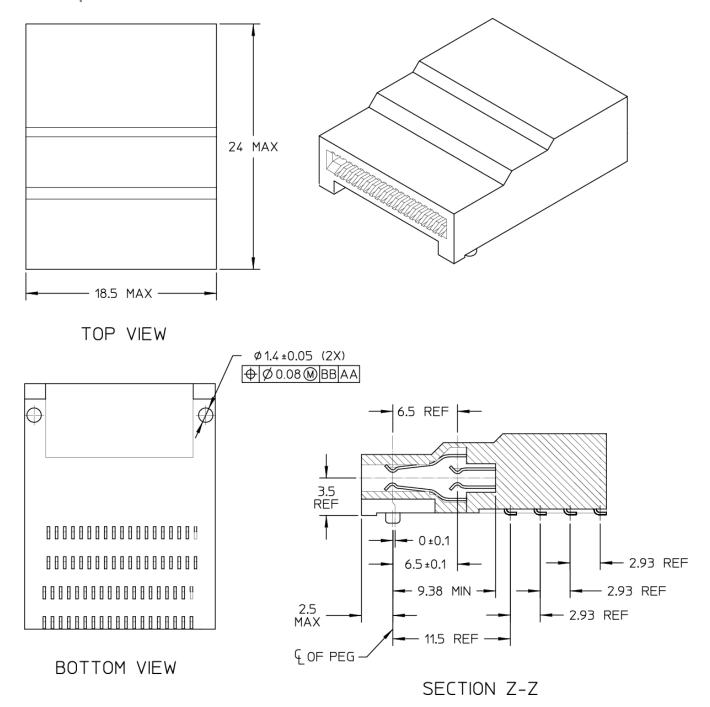

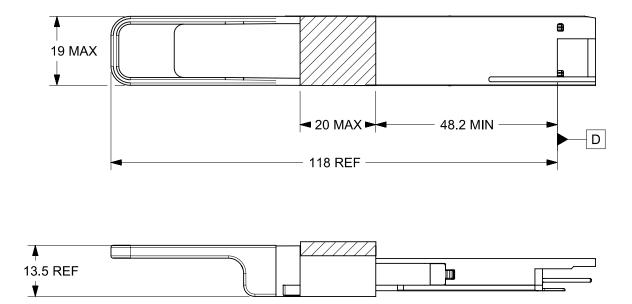

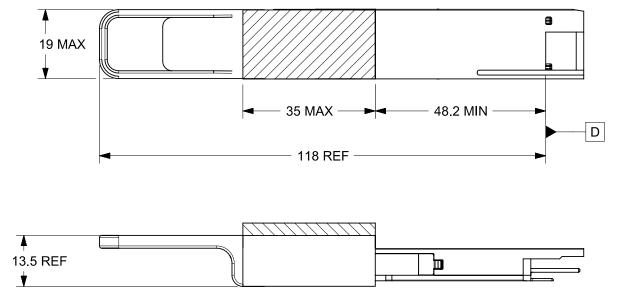

| 39 | 7.1 INTRODUCTION TO QSFP-DD/QSFP-DD800 MODULES                 |     |

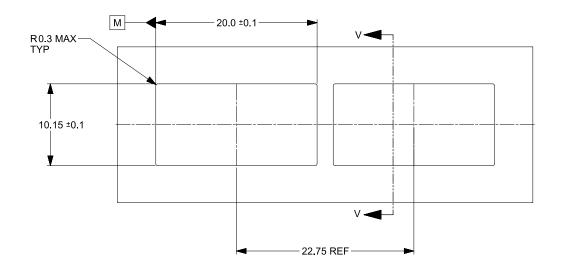

| 40 | 7.2 DATUMS, DIMENSIONS AND COMPONENT ALIGNMENT                 |     |

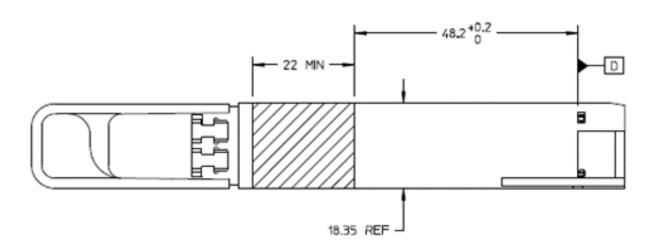

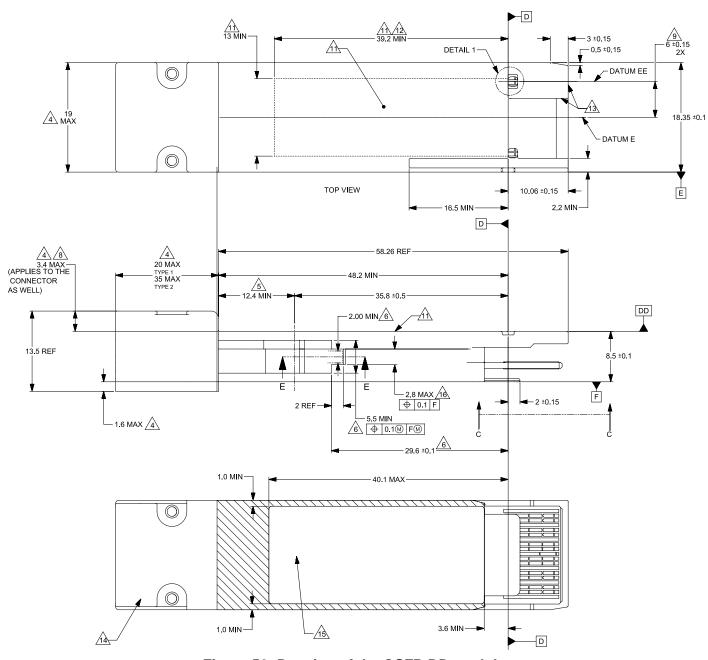

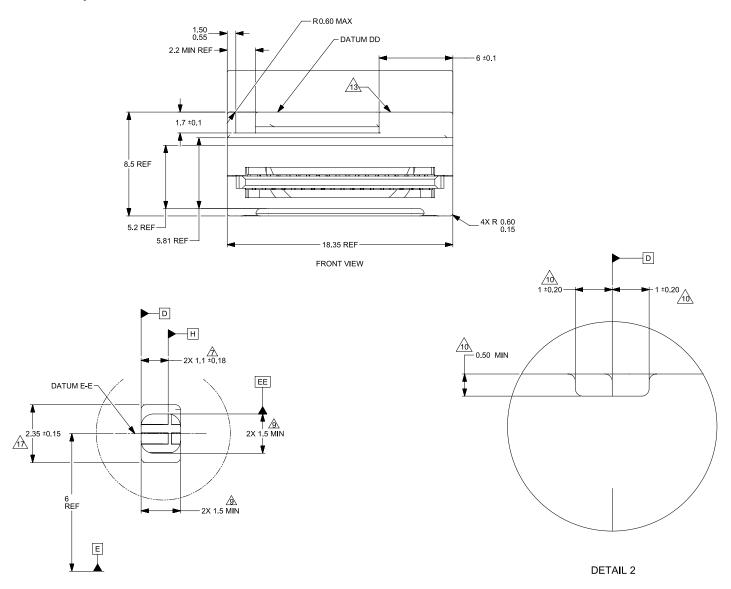

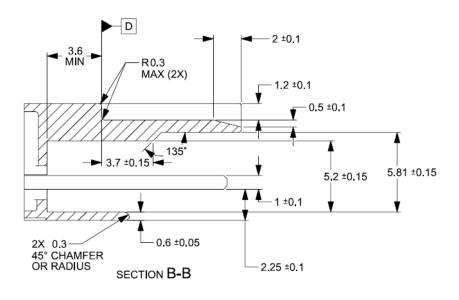

| 41 | 7.3 MODULE FORM FACTORS FOR QSFP-DD/QSFP-DD800                 |     |

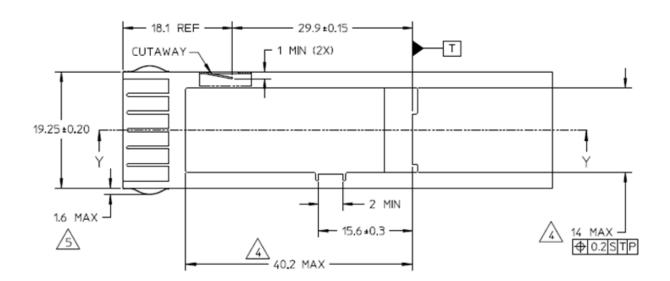

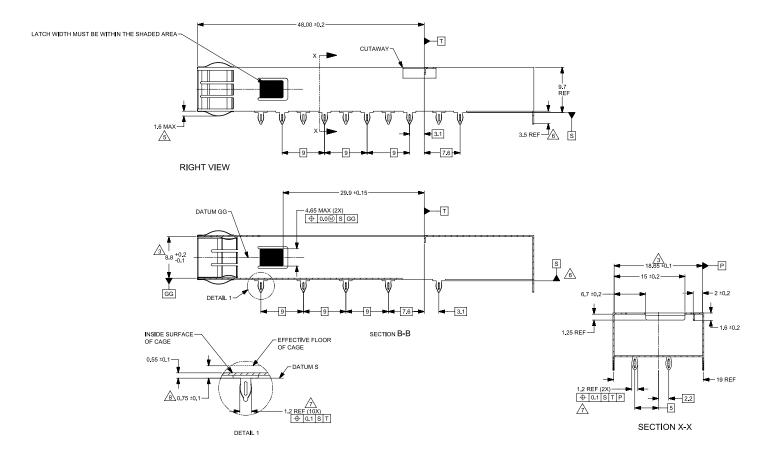

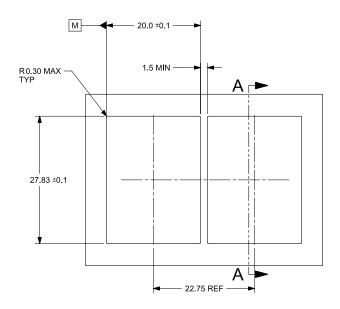

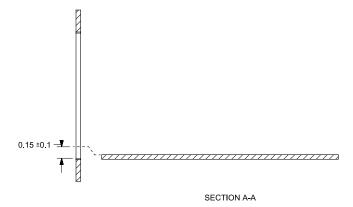

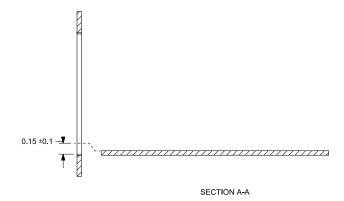

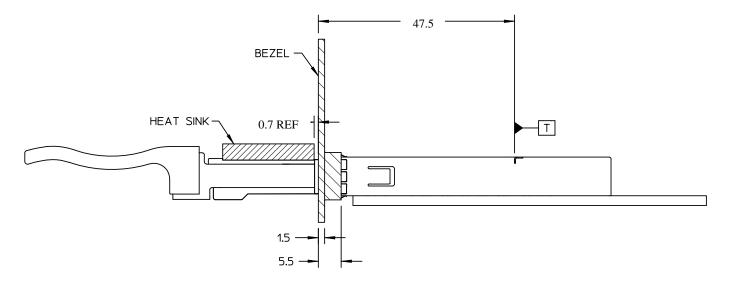

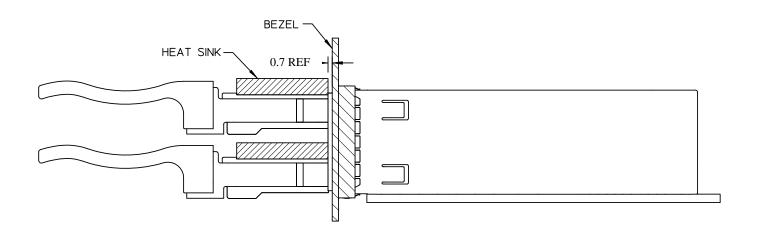

| 42 | 7.4 MODULE FLATNESS AND ROUGHNESS                              |     |

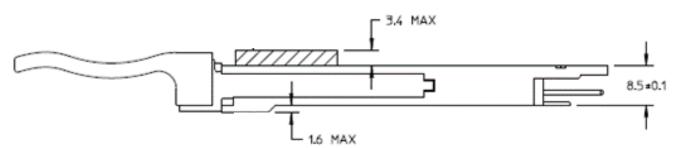

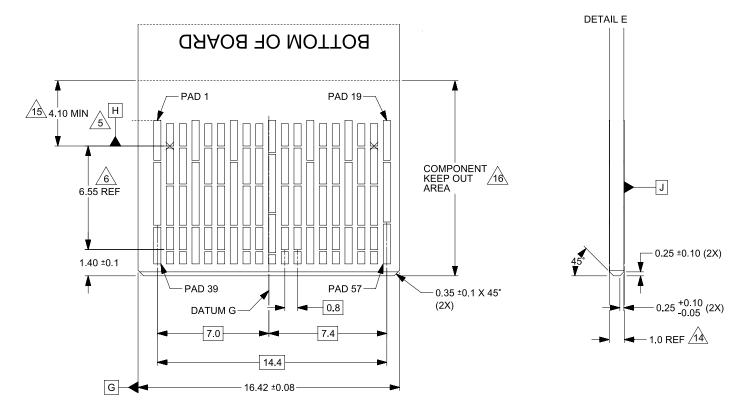

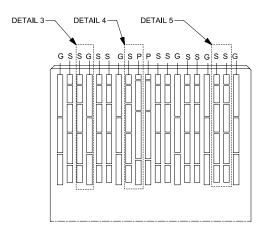

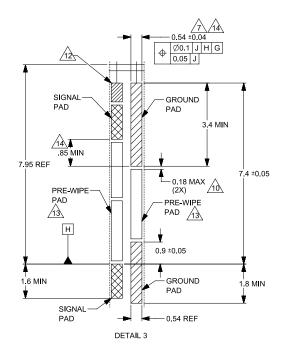

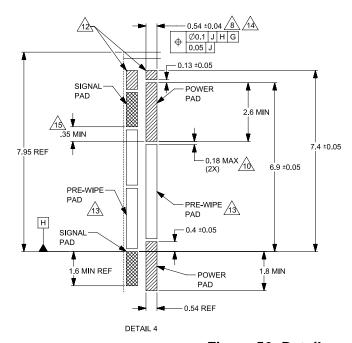

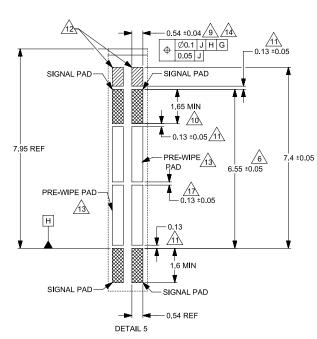

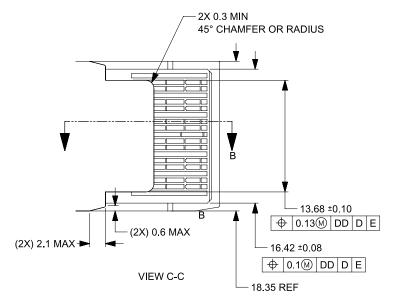

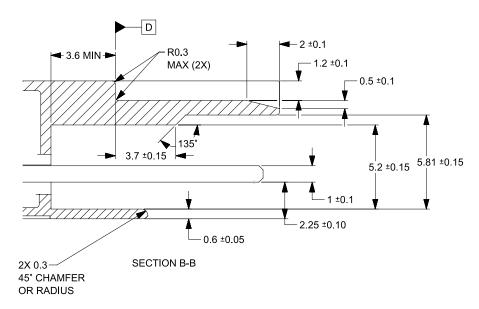

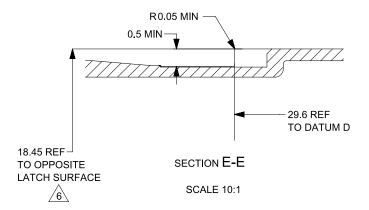

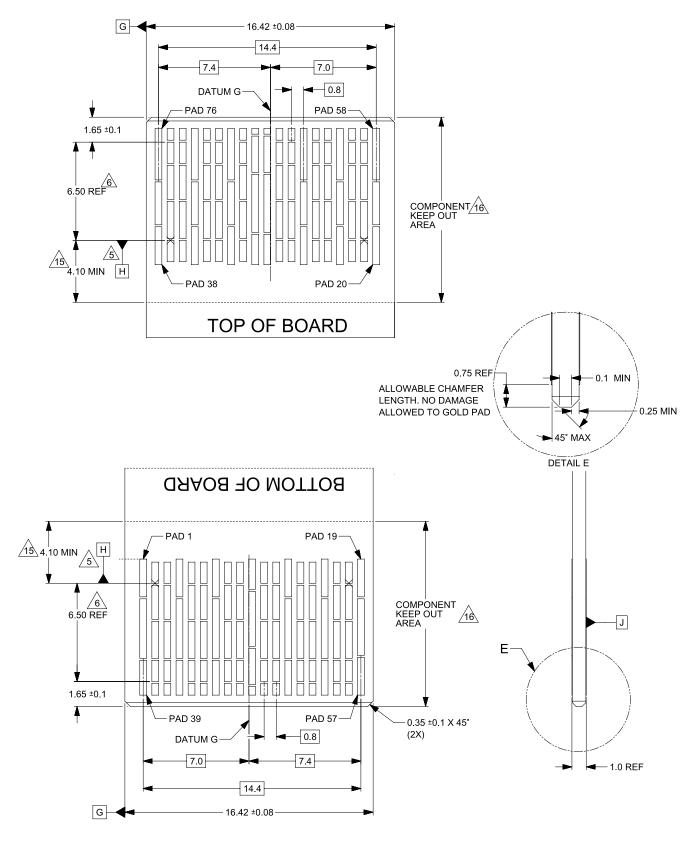

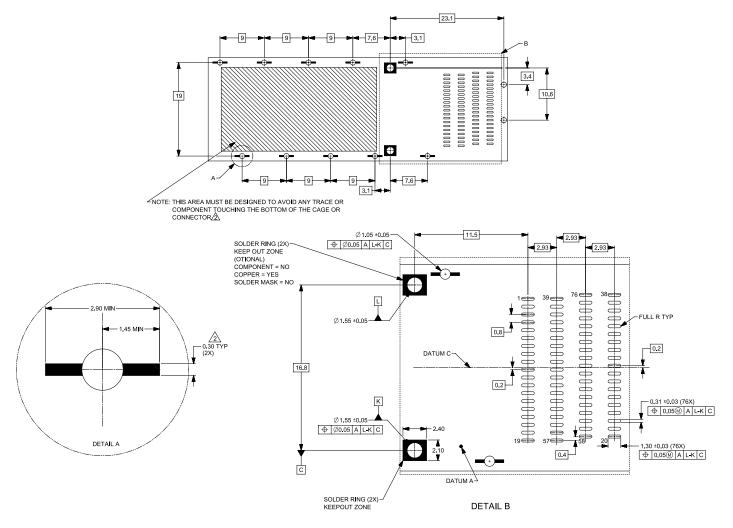

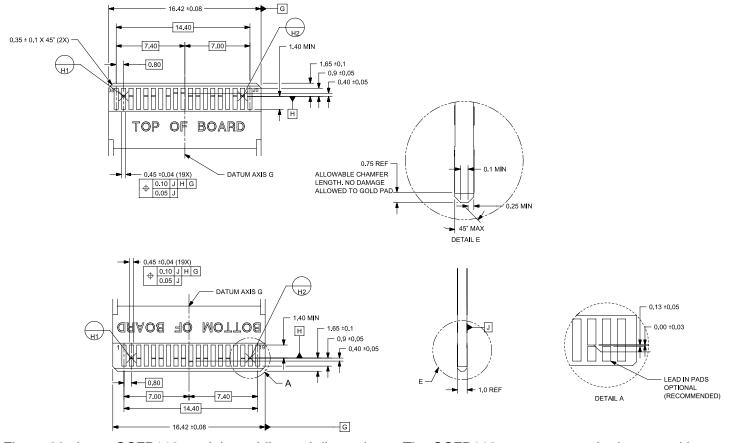

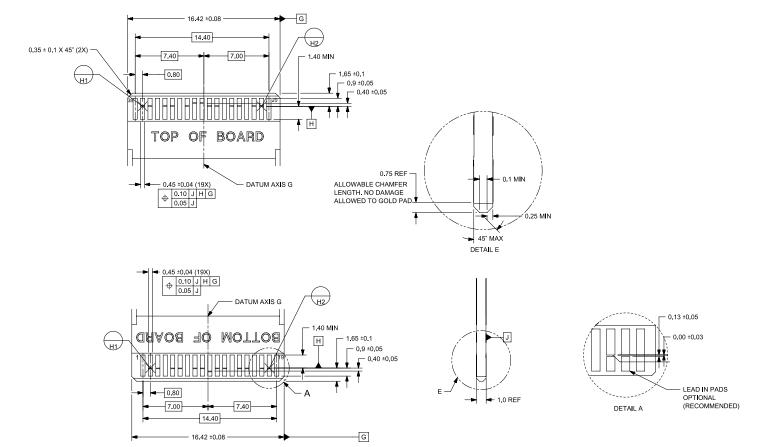

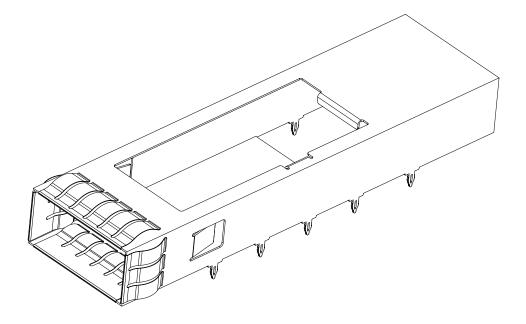

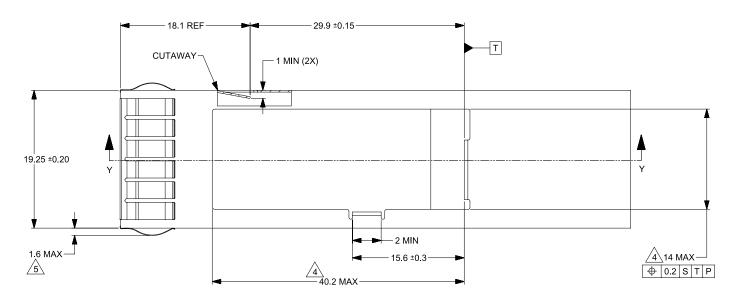

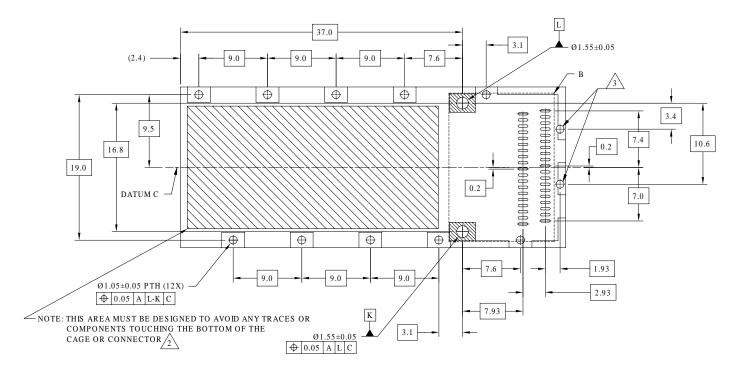

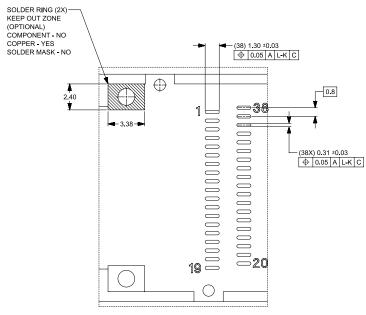

| 43 | 7.5 QSFP-DD MODULE PADDLE CARD DIMENSIONS NOTES                |     |

| 44 | 7.6 MODULE EXTRACTION AND RETENTION FORCES                     |     |

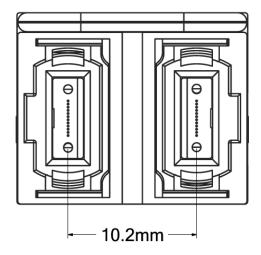

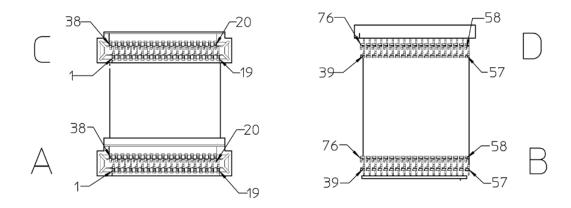

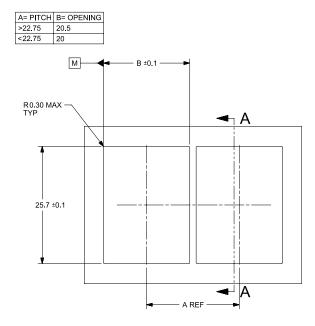

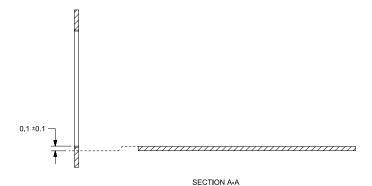

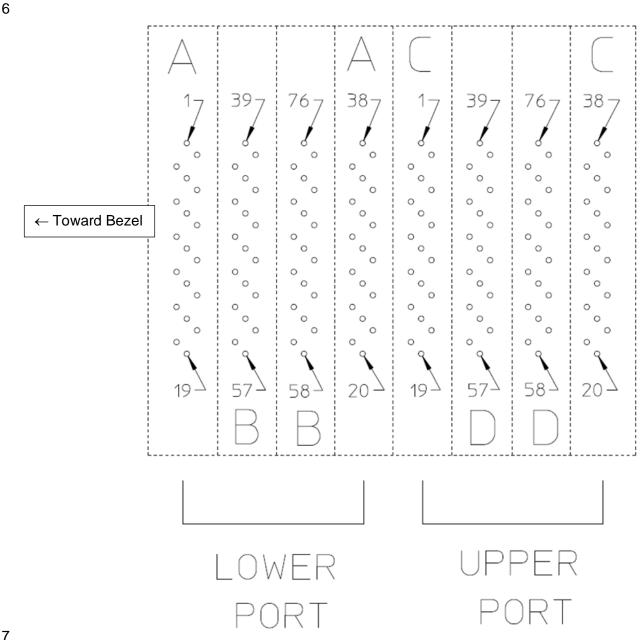

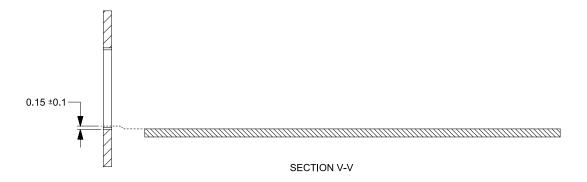

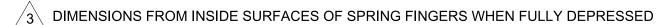

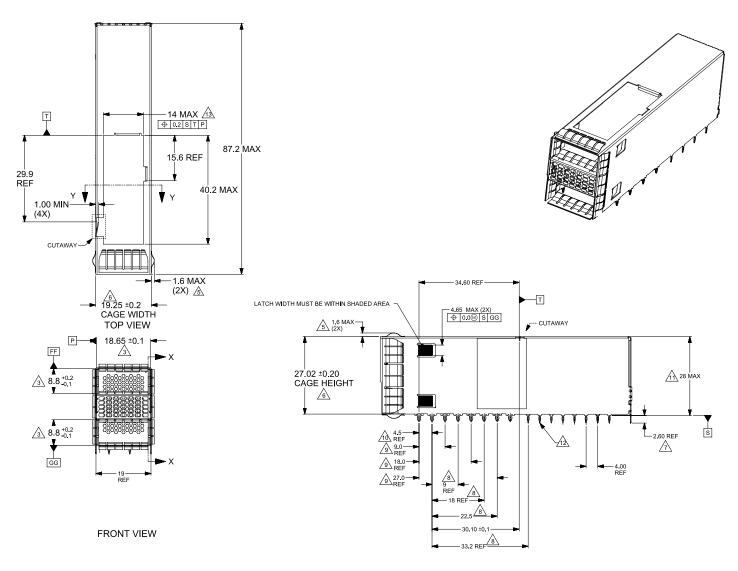

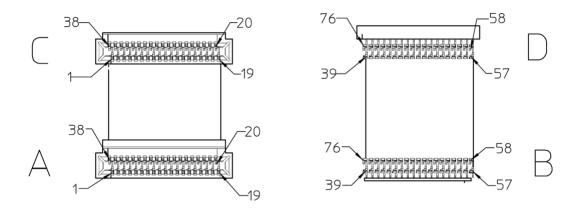

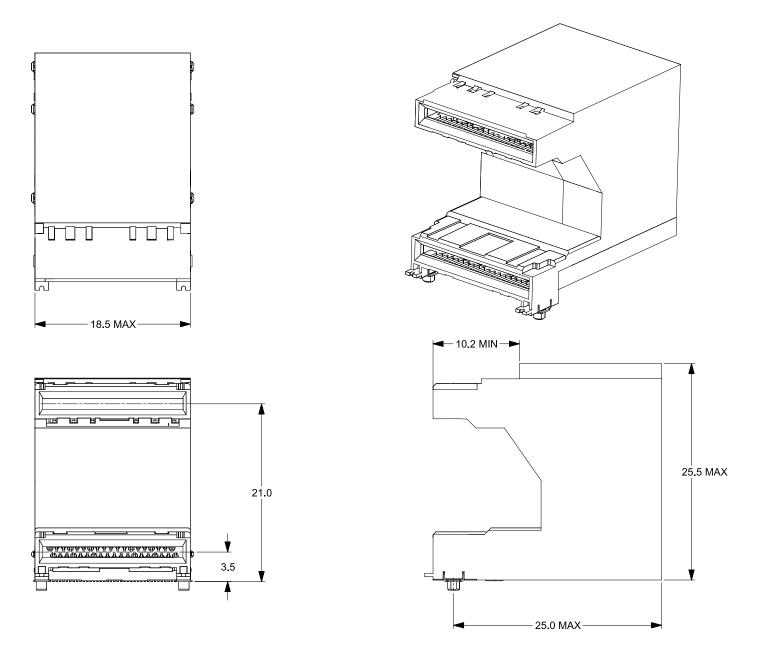

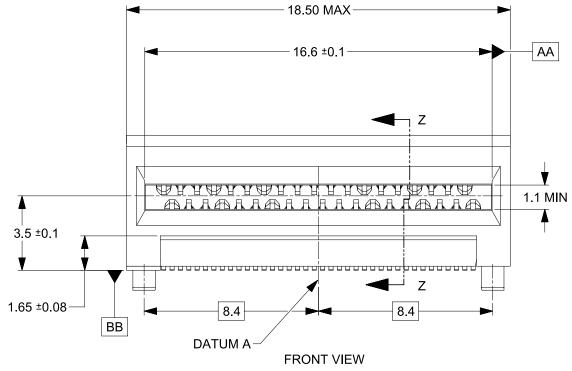

| 45 | 7.7 QSFP-DD 2x1 STACKED ELECTRICAL CONNECTOR MECHANICAL        |     |

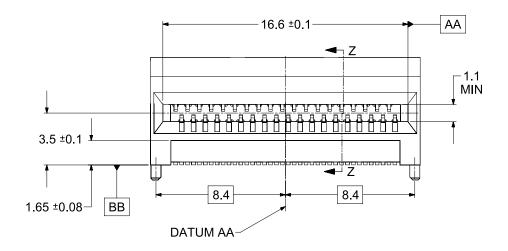

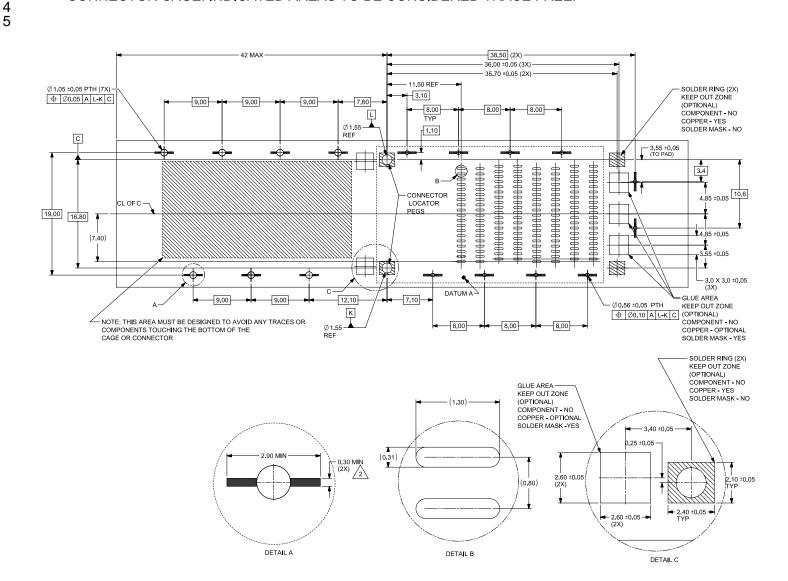

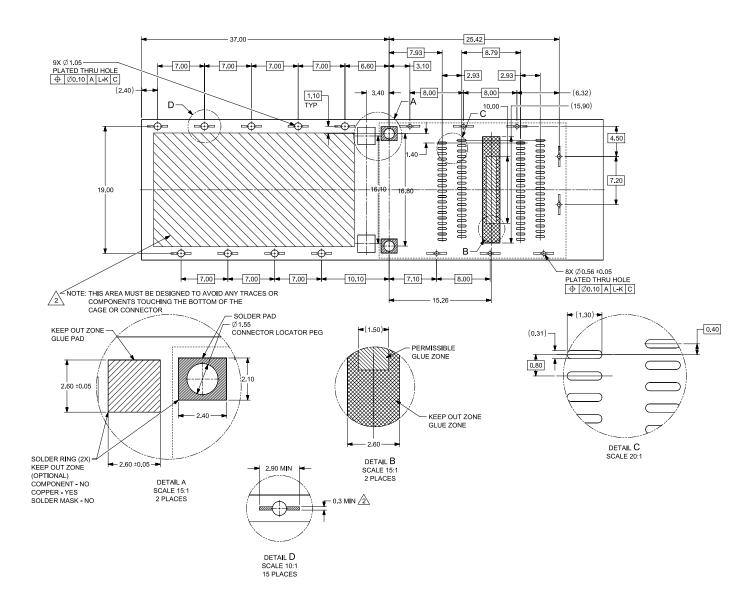

| 46 | 7.7.1 QSFP-DD 2x1 Connector and Cage host PCB layout           |     |

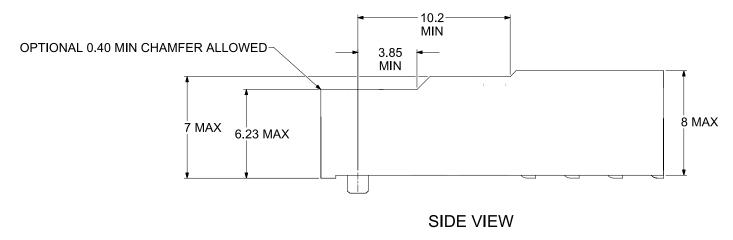

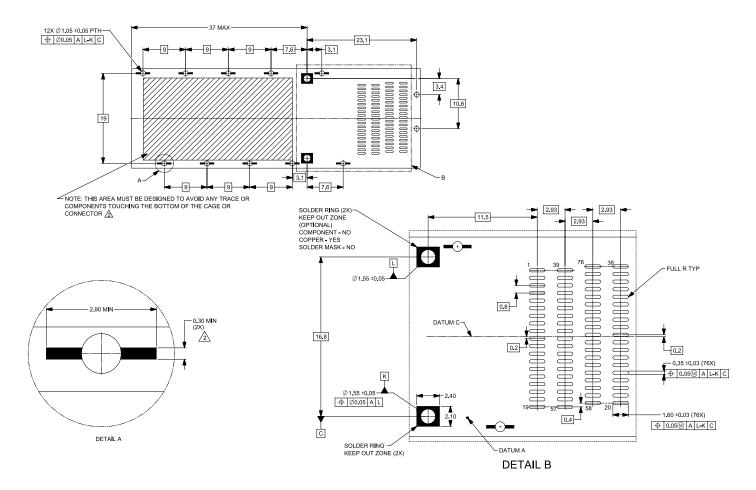

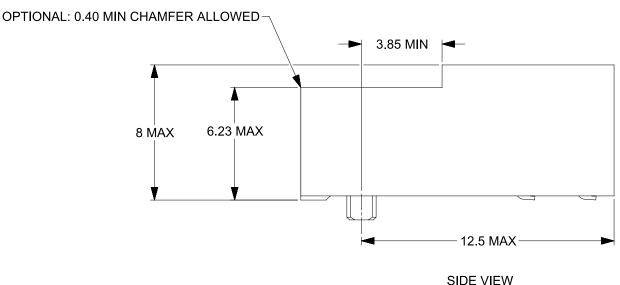

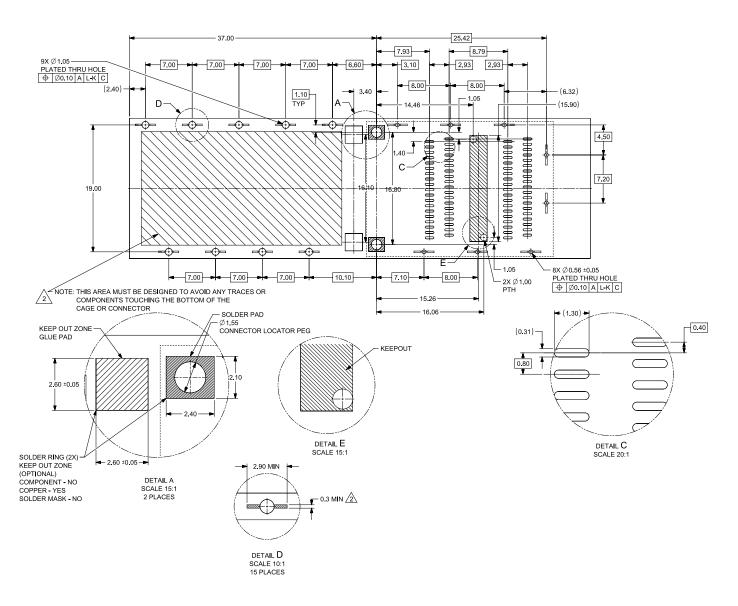

| 47 | 7.8 QSFP-DD SURFACE MOUNT ELECTRICAL CONNECTOR MECHANICAL      |     |

| 48 | 7.8.1 QSFP-DD Surface mount connector and cage host PCB layout | 109 |

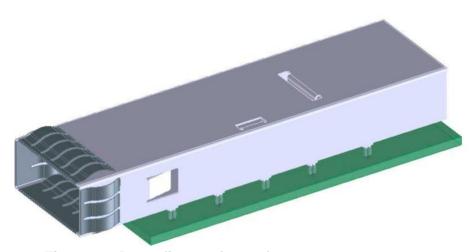

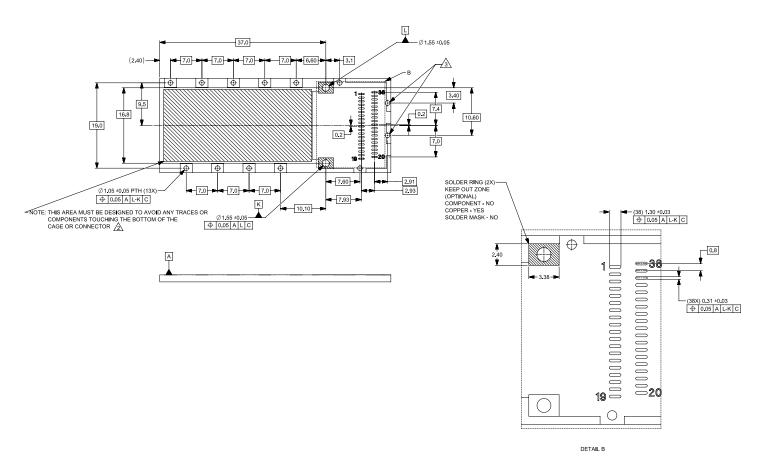

| 49 | 8 QSFP-DD800 MECHANICAL AND BOARD DEFINITION                   | 111 |

| 50 | 8.1 Introduction                                               | 111 |

| 51 | 8.2 QSFP-DD800 MODULE MECHANICAL DIMENSIONS                    |     |

| 52 | 8.3 QSFP-DD800 IMPROVED MODULE PADDLE CARD DIMENSIONS          |     |

| ~~ | 5.5 QGT   DDGGG IIII TO VED INODGEE   ADDEE GARD DINETIONONO   |     |

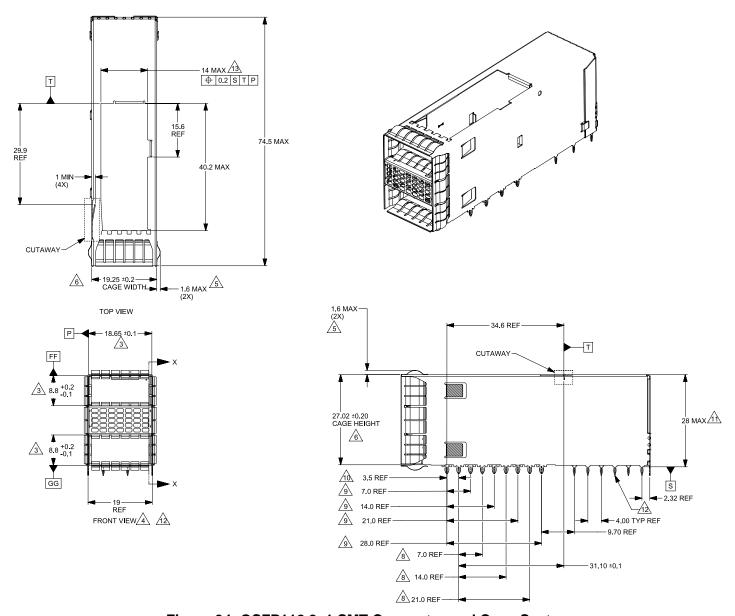

| 8.4   | QSFP-DD800 1x1 SMT connector/cage                                              | 119 |

|-------|--------------------------------------------------------------------------------|-----|

| 8.4   | 4.1 Surface mount connector and cage host PCB layout                           | 119 |

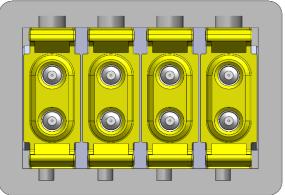

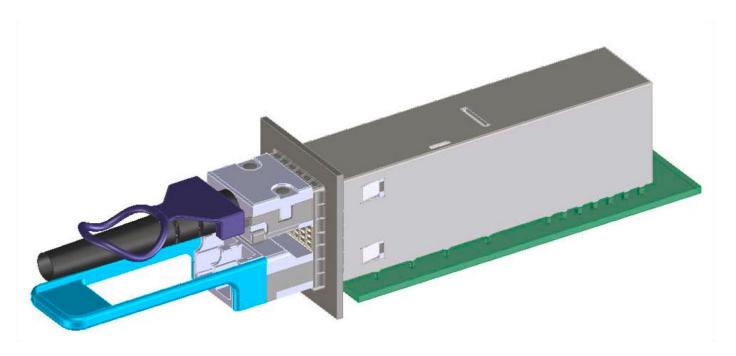

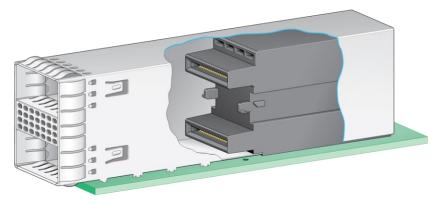

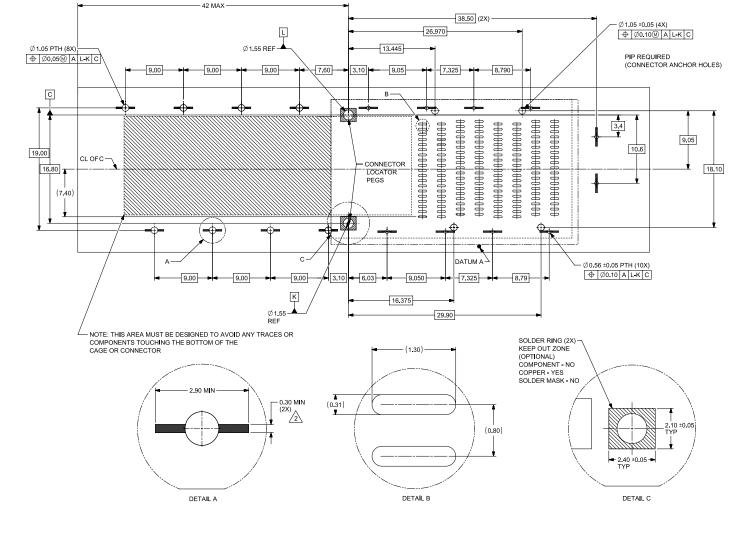

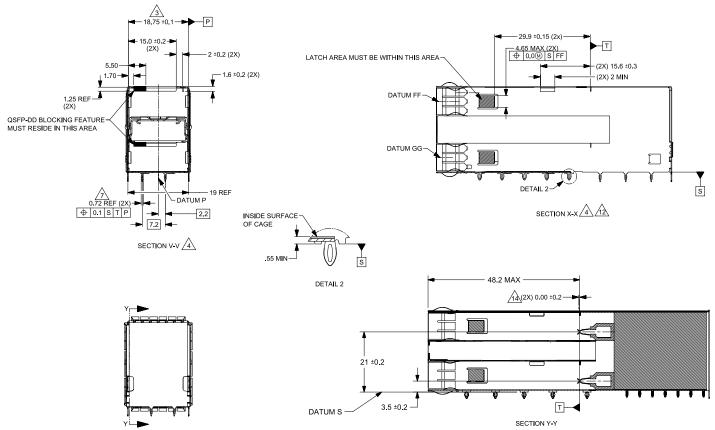

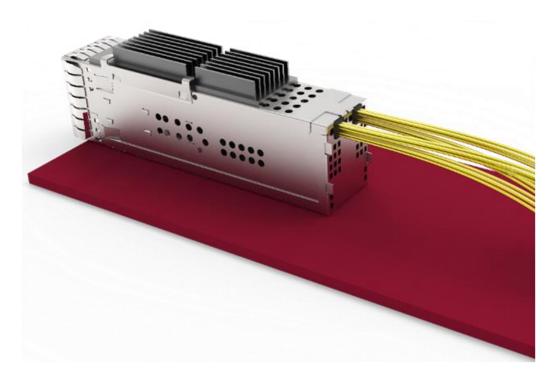

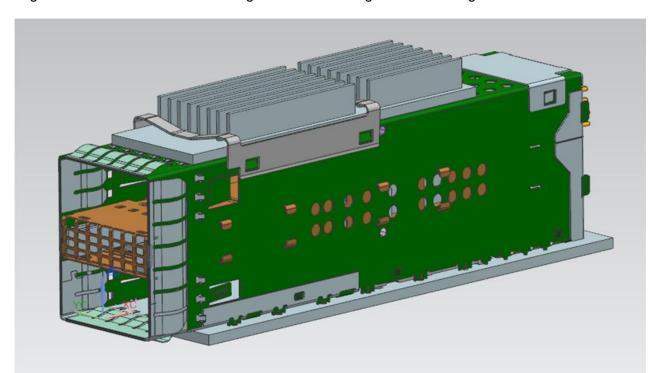

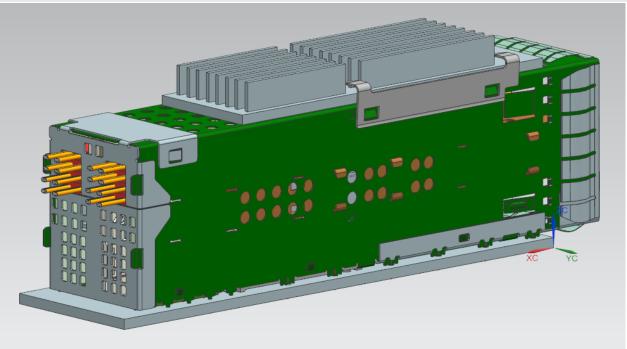

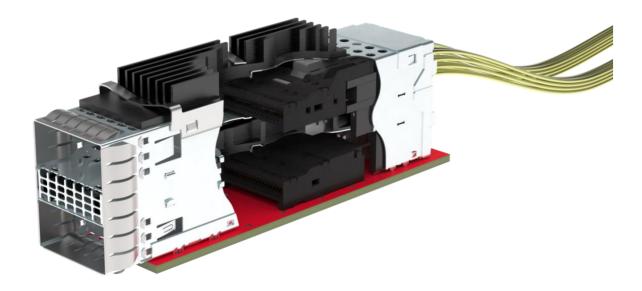

| 8.5   | 2x1 Surface Mount Technology (SMT) Connector/Cage                              | 120 |

| 8.8   | 5.1 2x1 SMT Connector/Cage System                                              | 120 |

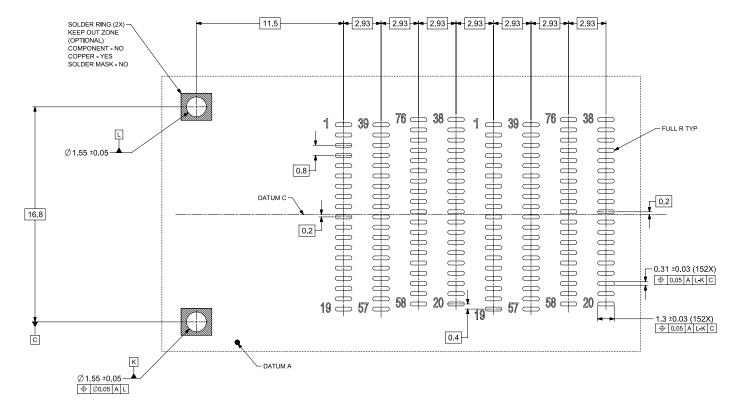

| 8.8   | 5.2 2x1 SMT Connector and Cage host PCB layout                                 | 125 |

| 9 QS  | SFP112 MECHANICAL AND BOARD DEFINITION                                         | 129 |

| 9.1   | Introduction                                                                   | 129 |

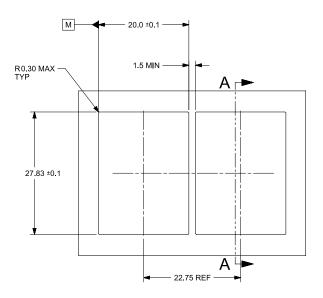

| 9.2   | QSFP112 MODULE MECHANICAL DIMENSIONS                                           |     |

| 9.3   | QSFP112 IMPROVED MODULE PADDLE CARD DIMENSIONS                                 | 129 |

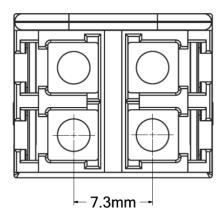

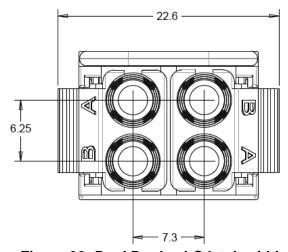

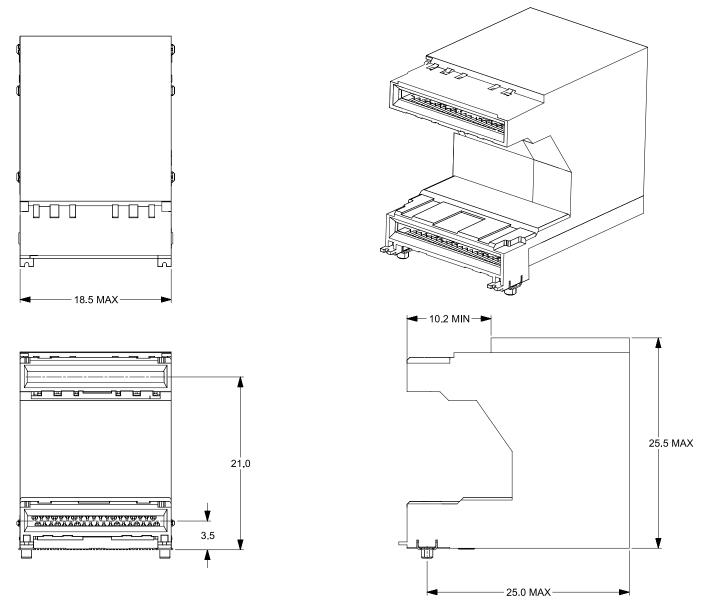

| 9.4   | QSFP112 1x1 SURFACE MOUNT CONNECTOR/CAGE                                       | 130 |

| 9.4   | 4.1 QSFP112 SMT host PCB layout                                                | 133 |

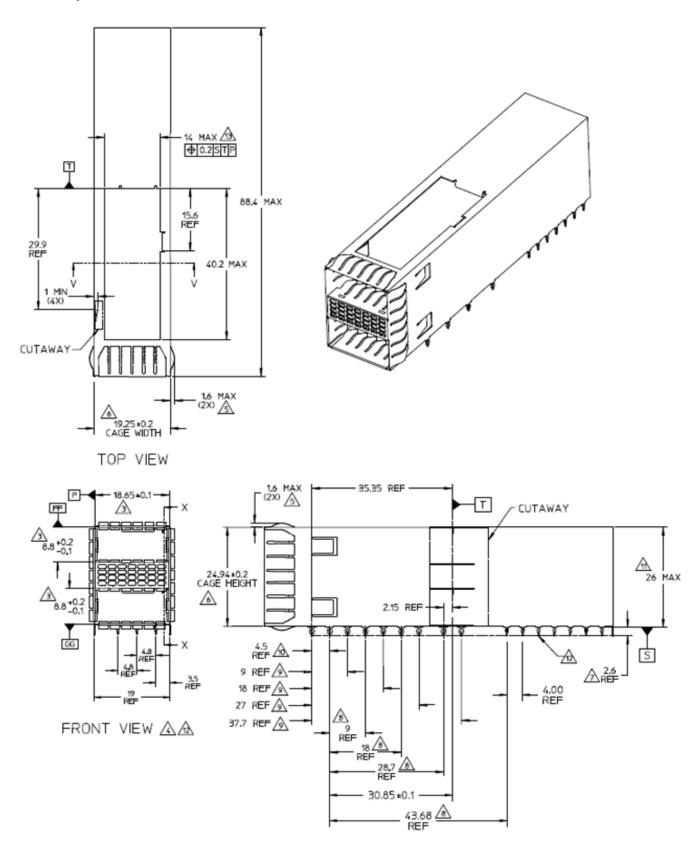

| 9.5   | QSFP112 2x1 STACKED SURFACE MOUNT CONNECTOR/CAGE                               | 136 |

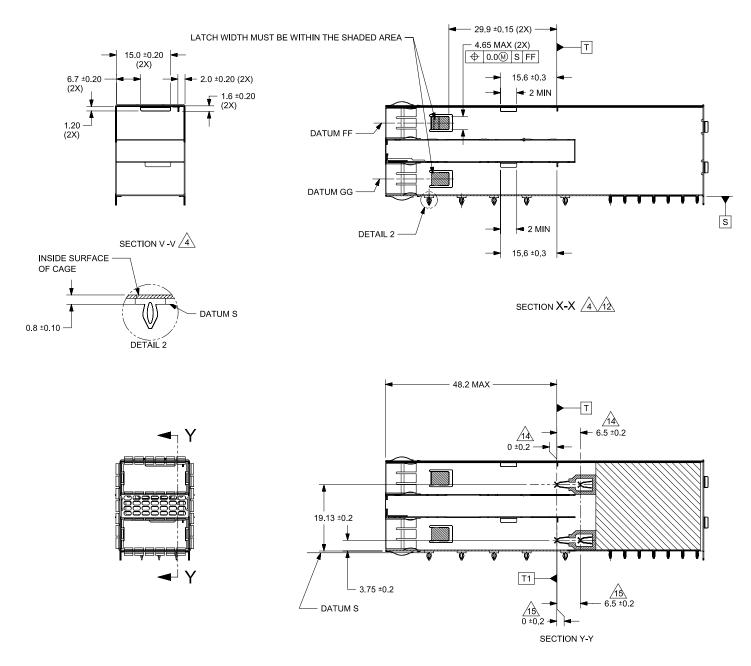

| 9.8   | 5.1 QSFP112 2x1 SMT host PCB layout                                            | 141 |

| 10    | MODULE ENVIRONMENTAL AND THERMAL REQUIREMENTS                                  | 144 |

| 10.1  | THERMAL REQUIREMENTS                                                           | 144 |

| 10.2  | THERMAL REQUIREMENTS - TIGHTER CONTROLLED ENVIRONMENTS                         | 144 |

| 10.3  | EXTERNAL CASE AND HANDLE TOUCH TEMPERATURE                                     | 144 |

| APPEN | IDIX A NORMATIVE MODULE AND CONNECTOR PERFORMANCE REQUIREMENTS                 | 145 |

| A.1   | QSFP-DD/QSFP-DD800 PERFORMANCE TABLES                                          | 145 |

| A.2   | Test                                                                           | 145 |

| APPEN | IDIX B INFORMATIVE OVERALL MODULE LENGTH WITH ELASTOMERIC HANDLE               | 149 |

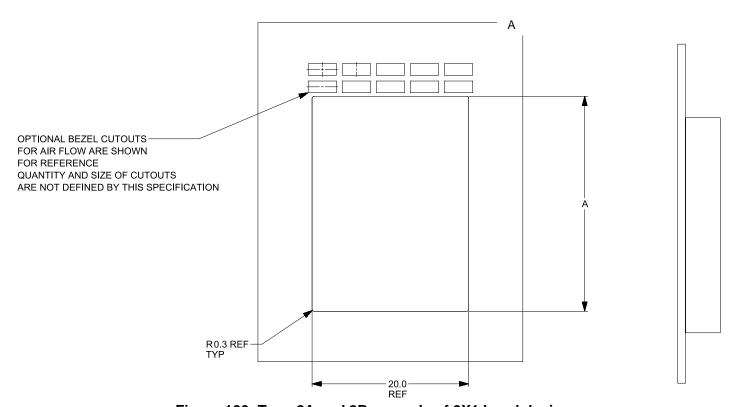

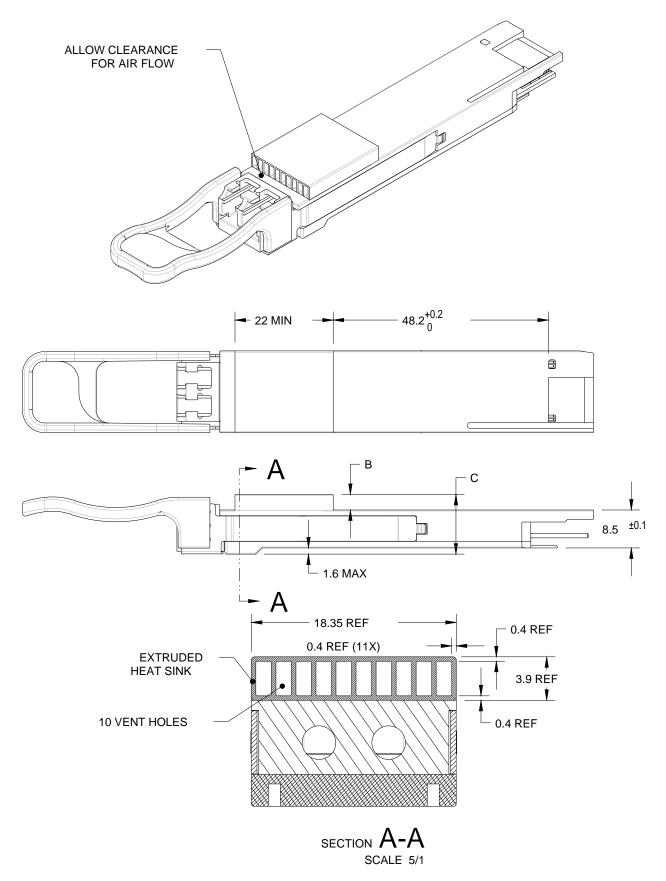

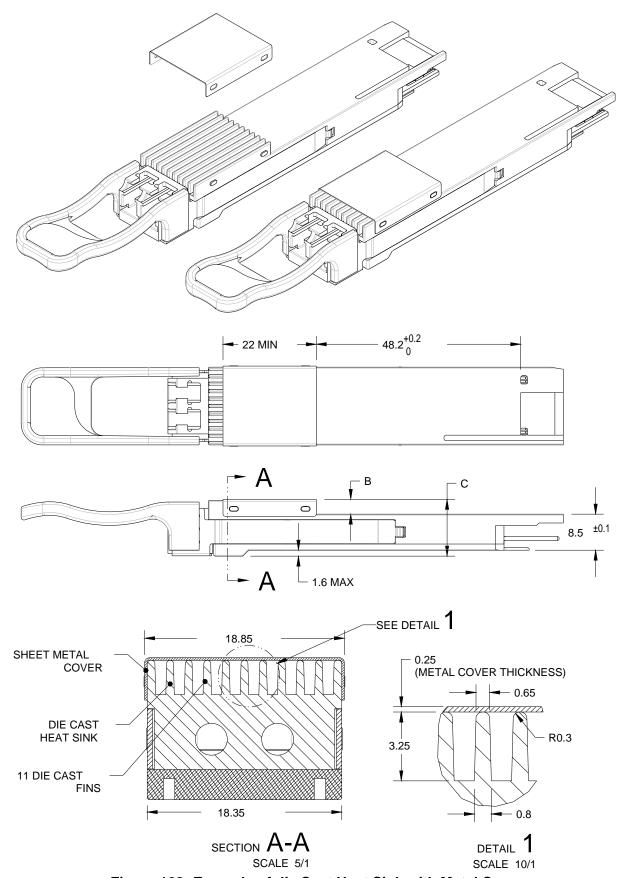

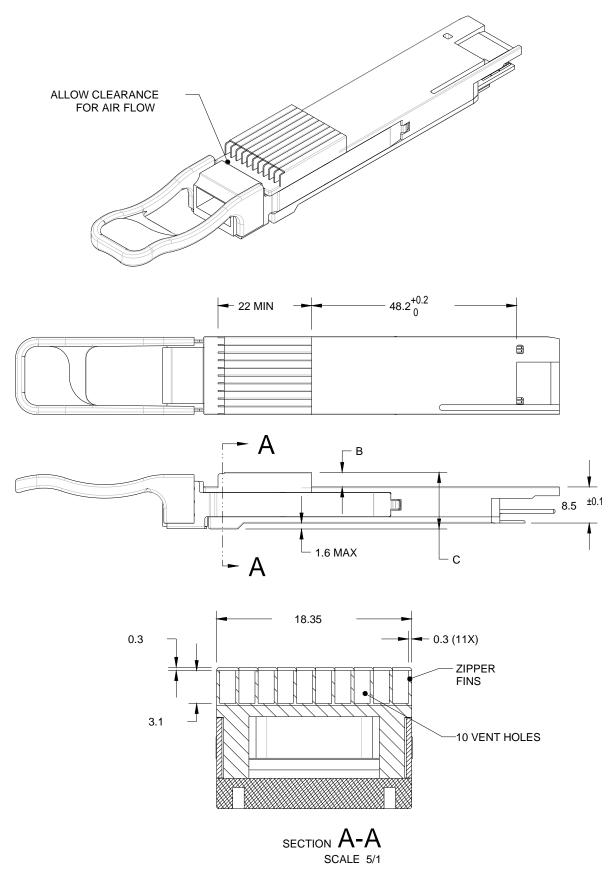

| APPEN | IDIX C INFORMATIVE QSFP-DD/QSFP-DD800 MODULE HEAT SINK TYPE 2A AND 2B EXAMPLES | 150 |

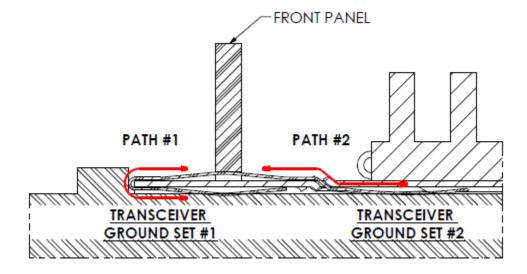

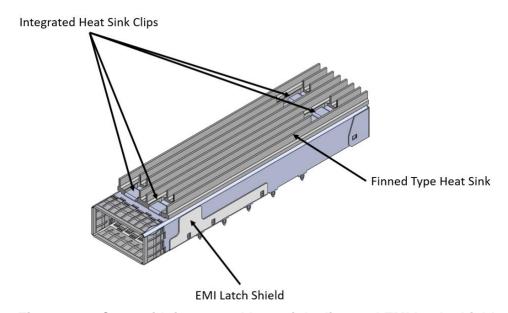

| APPEN | IDIX D QSFP-DD800 CAGE AND HEAT SINK MECHANISM AND EMI FINGERS                 | 157 |

| D.1   | Introduction                                                                   | 157 |

| D.2   | MECHANICAL DEFINITION                                                          |     |

| D.3   | EMI Spring Clip                                                                | 157 |

| D.4   | HEAT SINK ATTACH MECHANISM                                                     | 158 |

| D.5   | Host PCB Layout                                                                | 158 |

| D.6   | FRONT PANEL CUTOUT                                                             | 158 |

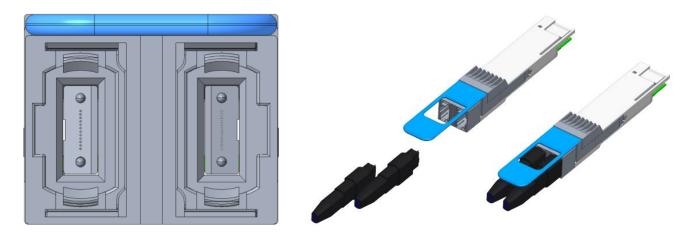

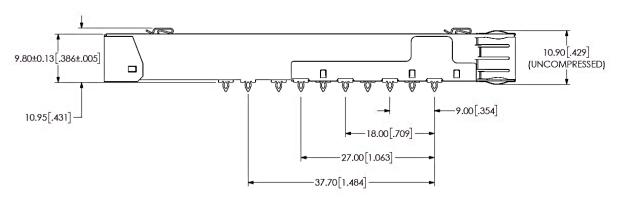

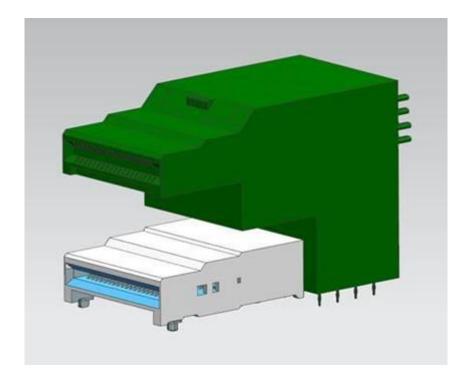

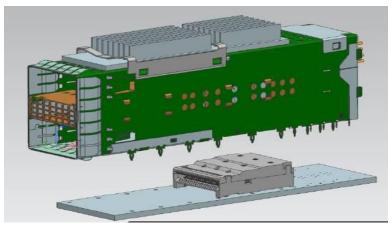

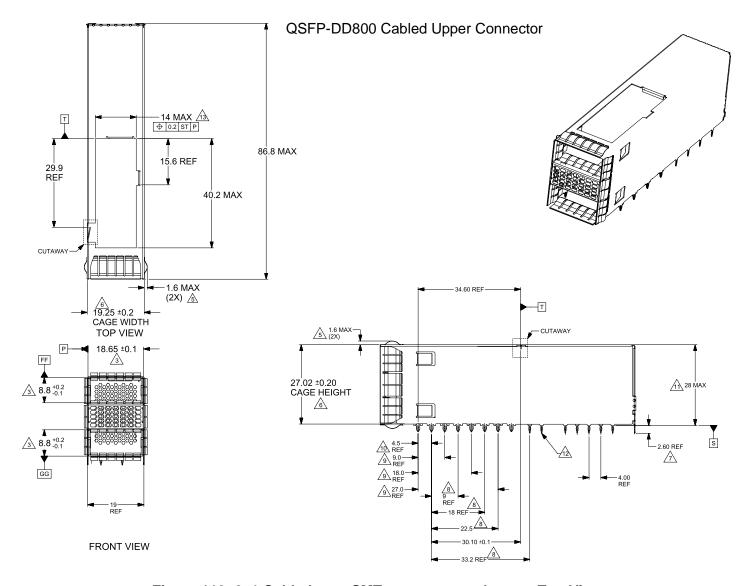

| APPEN | IDIX E INFORMATIVE QSFP-DD800 2X1 CABLED CONNECTOR AND CAGE                    | 159 |

| E.1   | 2x1 Cabled Upper Connector/Cage                                                | 159 |

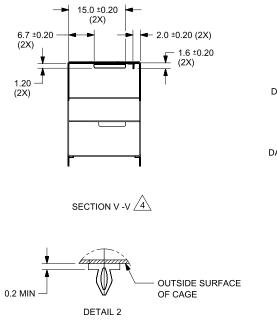

| E.2   | 2X1 CABLED CONNECTOR/CAGE ELECTRICAL CONNECTOR MECHANICAL                      | 160 |

| F 3   | 2x1 Carled Connector and Cage host PCR Layout                                  | 166 |

| 1        | List of Tables                                                                                   |     |  |  |  |

|----------|--------------------------------------------------------------------------------------------------|-----|--|--|--|

| 3        | Table 1- Pad Function Definition                                                                 | 18  |  |  |  |

| 4        | Table 2- ePPS/Clock Advertising Capabilities                                                     |     |  |  |  |

| 5        | Table 3- ePPS or Clock Modes                                                                     | 22  |  |  |  |

| 6        | Table 4- ePPS or Clock Frequency                                                                 | 22  |  |  |  |

| 7        | Table 5- Module ePPS/Clock Status Reporting (Required if module supports ePPS/Clock)             | 23  |  |  |  |

| 8        | Table 6- ePPS RF or Clock Frequency Reporting (Optional)                                         |     |  |  |  |

| 9        | Table 7- Low Speed Control and Sense Signals                                                     |     |  |  |  |

| 10       | Table 8- Management Interface timing parameters                                                  | 30  |  |  |  |

| 11       | Table 9- Timing for QSFP-DD soft control and status functions                                    |     |  |  |  |

| 12       | Table 10- I/O Timing for Squelch & Disable                                                       | 33  |  |  |  |

| 13       | Table 11- TX Squelch Levels                                                                      | 34  |  |  |  |

| 14       | Table 12- Power Classes                                                                          | 35  |  |  |  |

| 15       | Table 13- Power supply specifications, instantaneous, sustained, and steady state current limits | 37  |  |  |  |

| 16       | Table 14- Power Supply Output Noise and Tolerance Specifications                                 | 40  |  |  |  |

| 17       | Table 15- QSFP112 Pad Function Definition                                                        |     |  |  |  |

| 18       | Table 16- Low Speed Control and Sense Signals                                                    | 51  |  |  |  |

| 19       | Table 17- Management Interface timing parameters                                                 | 54  |  |  |  |

| 20       | Table 18- Timing for QSFP112 soft control and status functions                                   |     |  |  |  |

| 21       | Table 19- I/O Timing for Squelch & Disable                                                       | 59  |  |  |  |

| 22       | Table 20- QSFP112 Power Classes                                                                  | 61  |  |  |  |

| 23       | Table 21- Power supply specifications, instantaneous, sustained, and steady state current limits | 63  |  |  |  |

| 24       | Table 22- Truncated Filter Response Coefficients for Host Power Supply Noise Output              | 65  |  |  |  |

| 25       | Table 23- Power Supply Output Noise and Tolerance Specifications                                 |     |  |  |  |

| 26       | Table 24- Electrical Signal to Optical Port Mapping                                              | 68  |  |  |  |

| 27       | Table 25- Datums                                                                                 |     |  |  |  |

| 28       | Table 26- QSFP-DD/QSFP-DD800 Module flatness specifications                                      | 92  |  |  |  |

| 29       | Table 27- QSFP112 Module flatness specifications                                                 | 92  |  |  |  |

| 30       | Table 28- Optional Enhanced Module flatness specifications                                       | 92  |  |  |  |

| 31       | Table 29- Temperature Range Class of operation                                                   | 144 |  |  |  |

| 32       | Table 30- Temperature Range Classes for Tighter Controlled Applications                          | 144 |  |  |  |

| 33       | Table 31- Form Factor Performance Requirements                                                   |     |  |  |  |

| 34       | Table 32- EIA-364-1000 Test Details                                                              |     |  |  |  |

| 35       | Table 33- Additional Test Procedures                                                             |     |  |  |  |

| 36       | Table 34- Dimensions for QSFP-DD/QSFP-DD800 and Module Type 2A/2B                                | 150 |  |  |  |

| 37       |                                                                                                  |     |  |  |  |

| 38<br>39 | List of Figures                                                                                  |     |  |  |  |

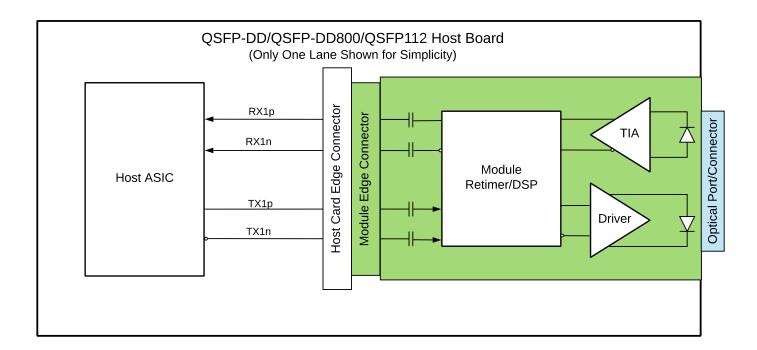

| 40       | Figure 1: Application Reference Model                                                            | 14  |  |  |  |

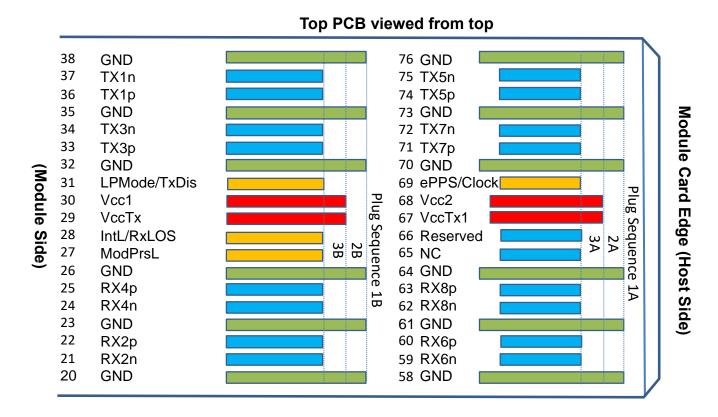

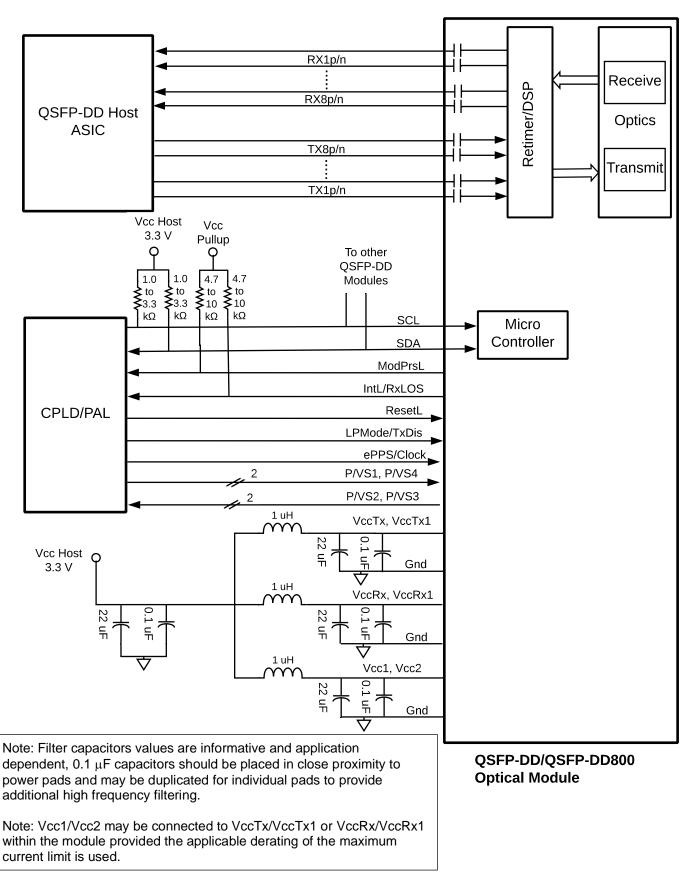

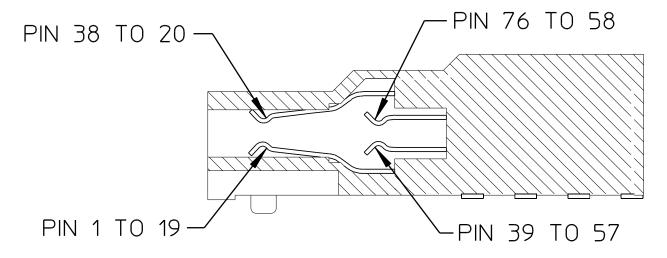

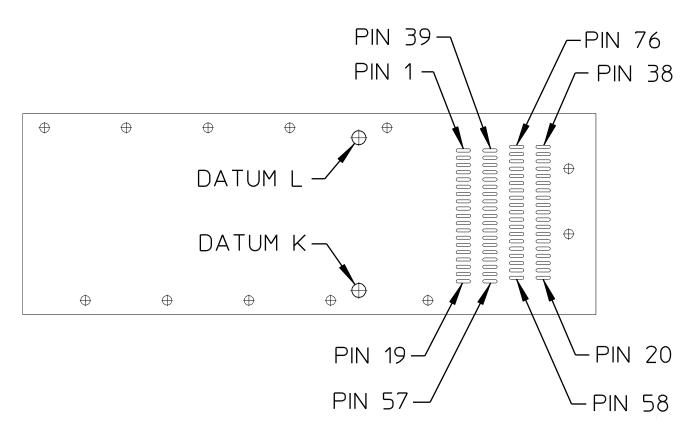

| 41       | Figure 2: Module pad assignment and layout                                                       |     |  |  |  |

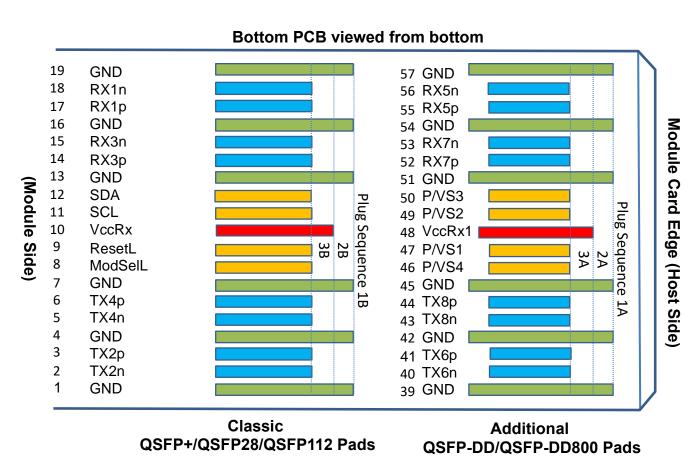

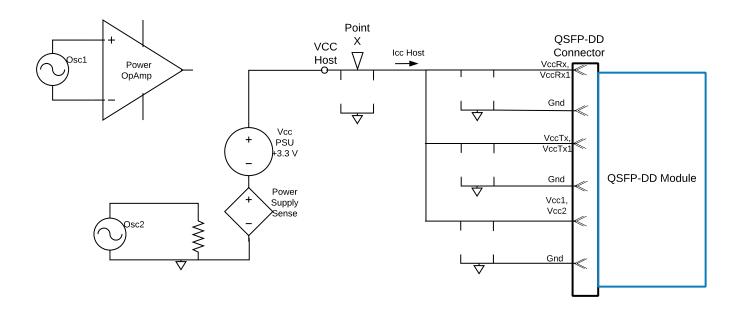

| 42       | Figure 3: Example QSFP-DD/QSFP-DD800 host board schematic for Optical Modules                    |     |  |  |  |

| 43       | Figure 4: Example QSFP-DD/QSFP-DD800 host board schematic for Active Copper Cables Module        |     |  |  |  |

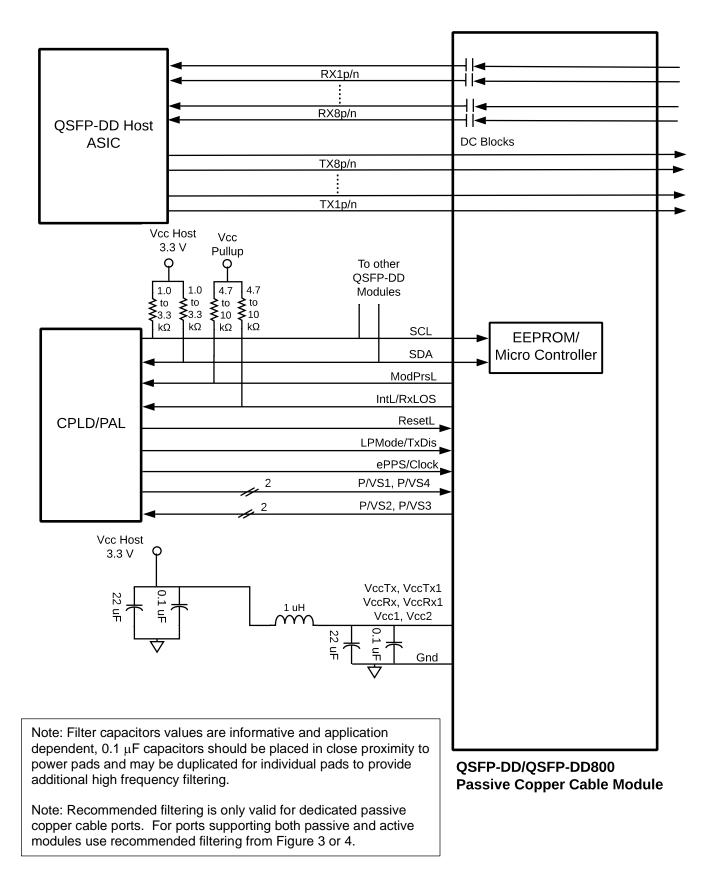

| 44       | Figure 5: Example QSFP-DD/QSFP-DD800 host board schematic of Passive Copper Cables Module.       |     |  |  |  |

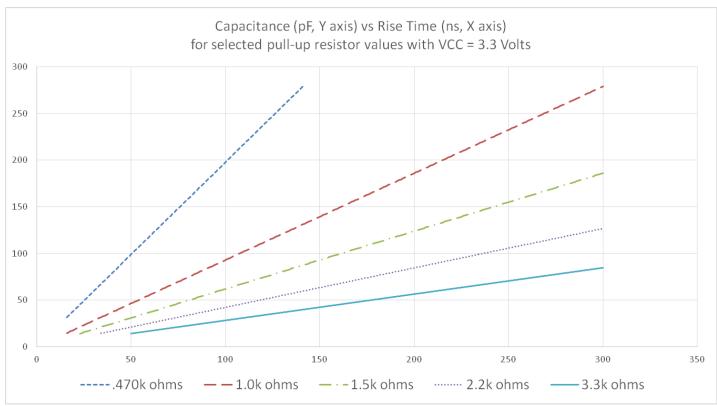

| 45       | Figure 6: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times              |     |  |  |  |

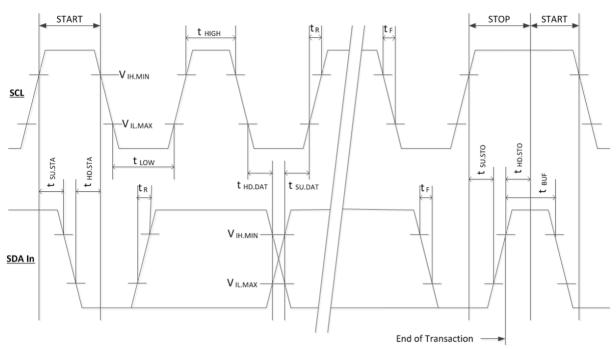

| 46       | Figure 7: TWI Timing Diagram                                                                     |     |  |  |  |

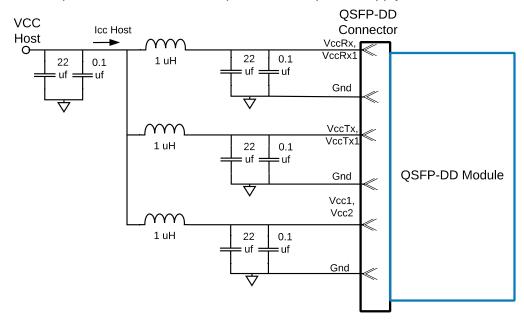

| 47       | Figure 8: Reference Power Supply Filter for Module Testing                                       |     |  |  |  |

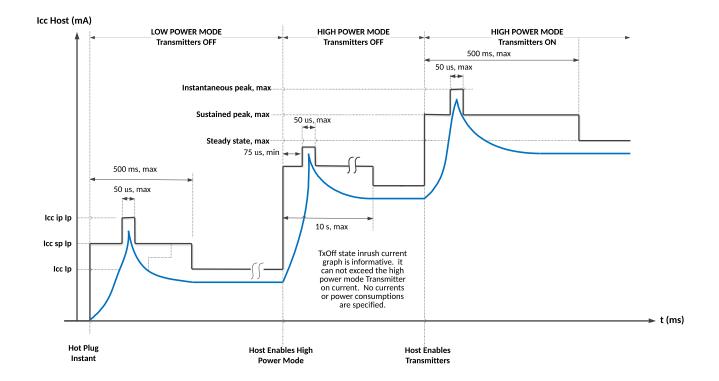

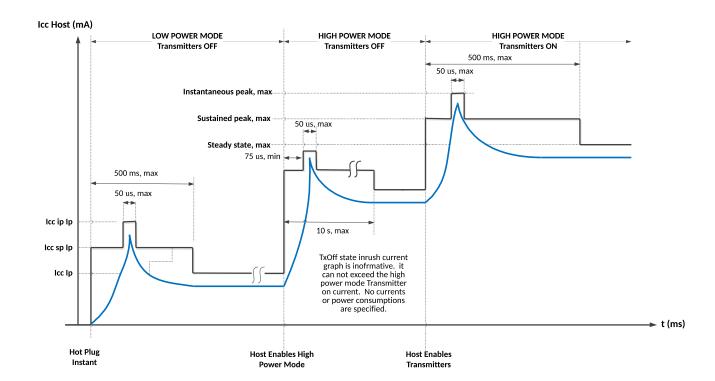

| 48       | Figure 9: Instantaneous and sustained peak currents for Icc Host (see Table 13)                  |     |  |  |  |

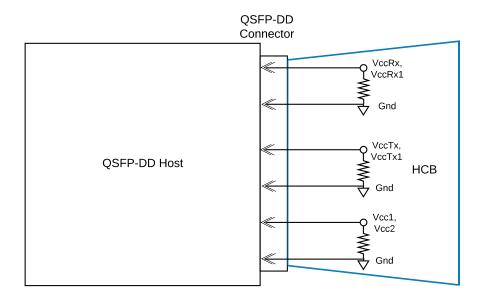

| 49       | Figure 10: Host Noise Output Measuremnt                                                          |     |  |  |  |

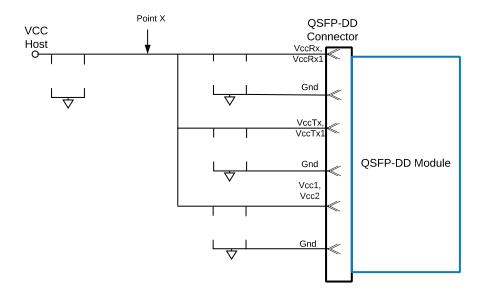

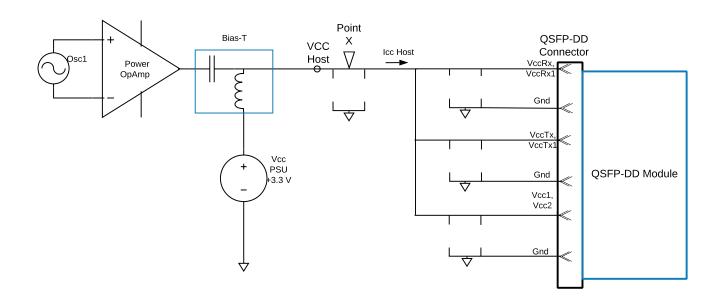

| 50       | Figure 11: Module Noise Output Measuremnt                                                        |     |  |  |  |

| 51       | Figure 12: Module High Frequency Noise Tolerance                                                 |     |  |  |  |

| 52       | Figure 13: Module Low Frequency Noise Tolerance                                                  |     |  |  |  |

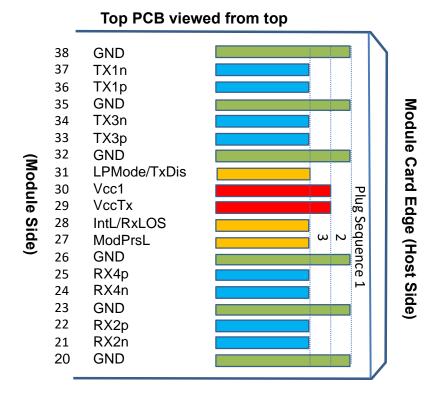

| 53       | Figure 14: QSFP112 module pad assignment and layout                                              |     |  |  |  |

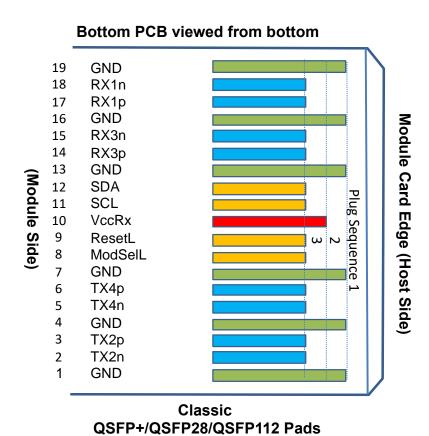

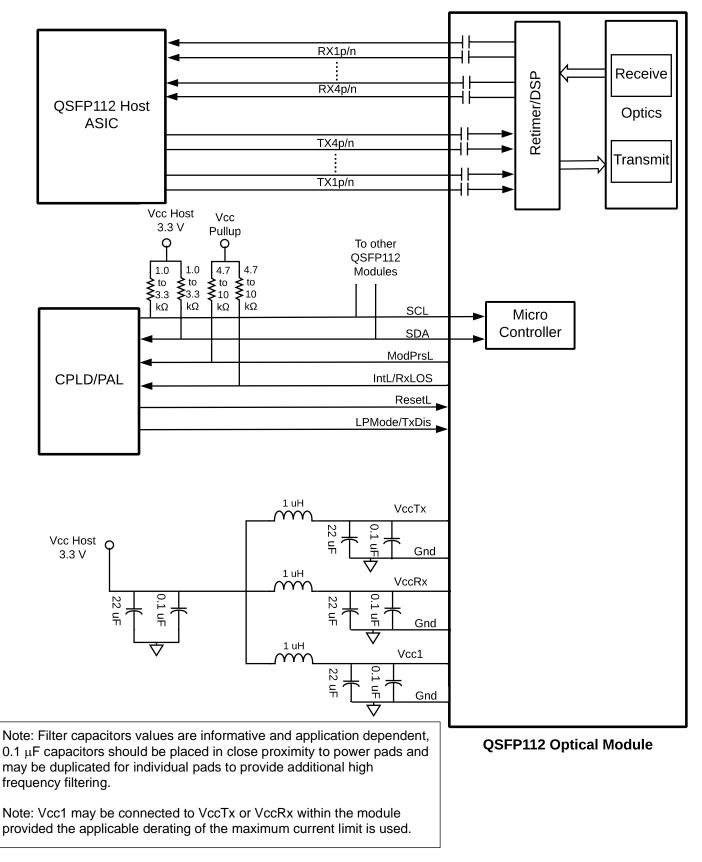

| 54       | Figure 15: Example QSFP112 Host Board Schematic for Optical Modules                              |     |  |  |  |

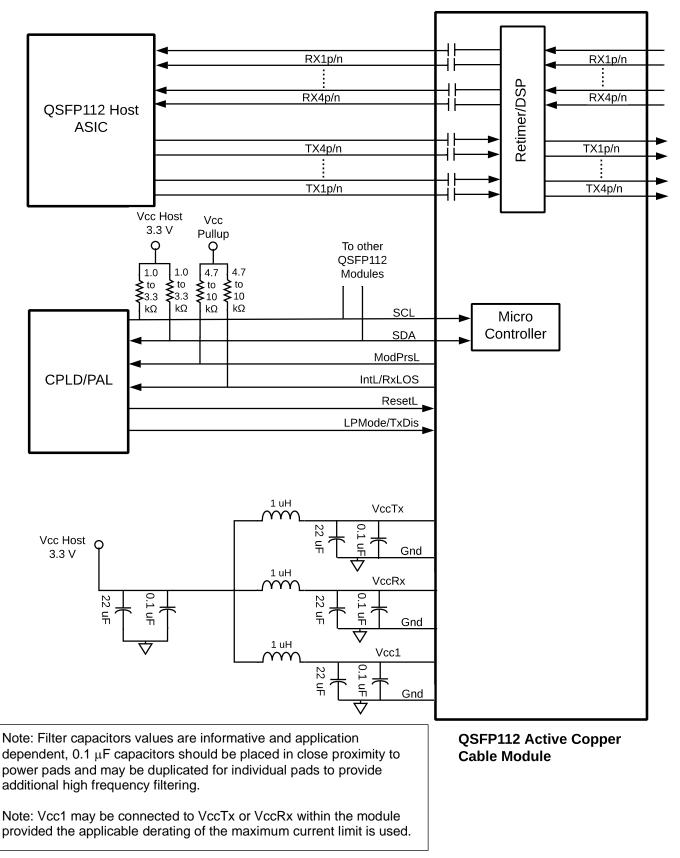

| 1  | Figure 16: Example QSFP112 host board schematic for Active Copper Cable Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

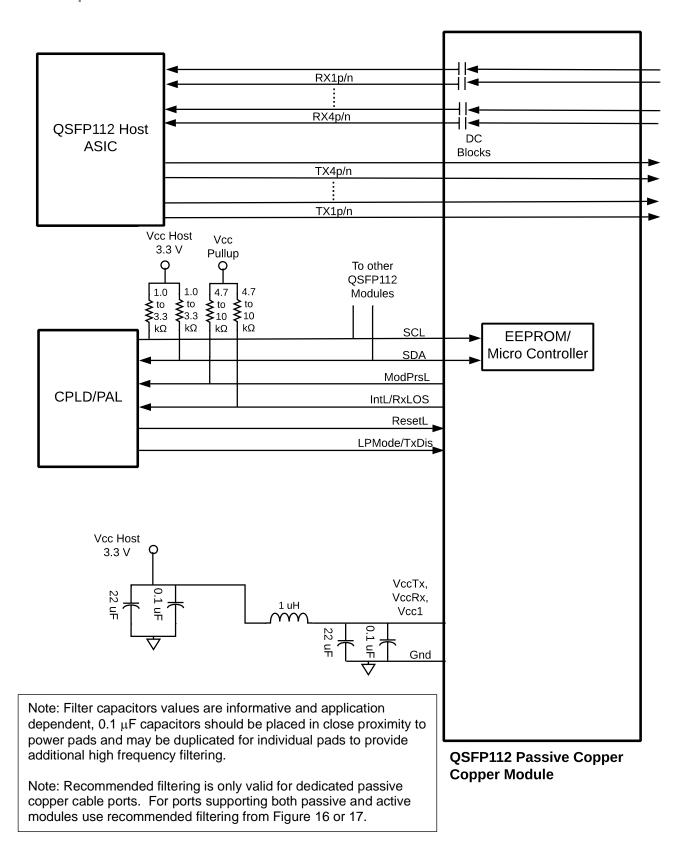

| 2  | Figure 17: Example QSFP112 Host Board Schematic for Passive Copper Cable Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

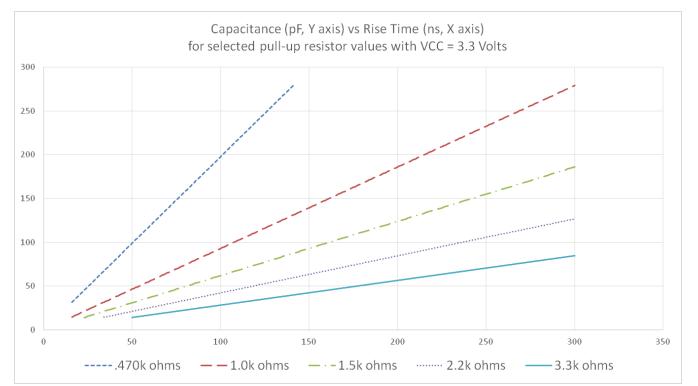

| 3  | Figure 18: SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

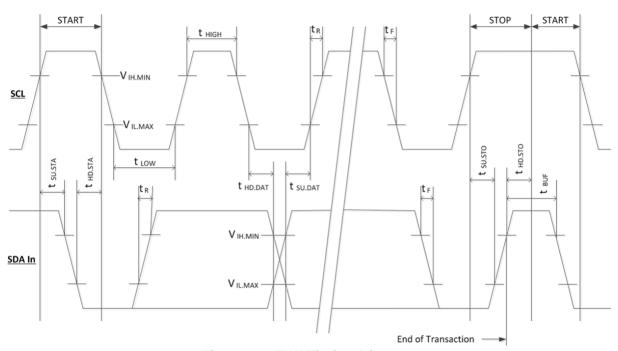

| 4  | Figure 19: TWI Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

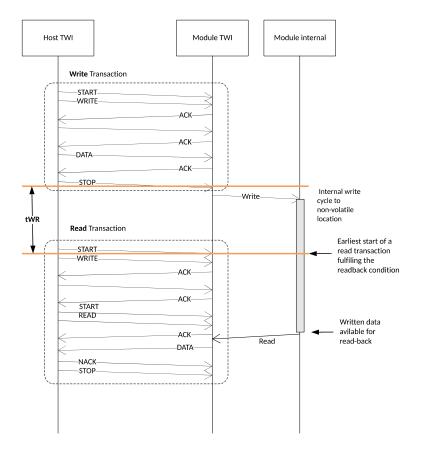

| 5  | Figure 20: Bus timing tWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

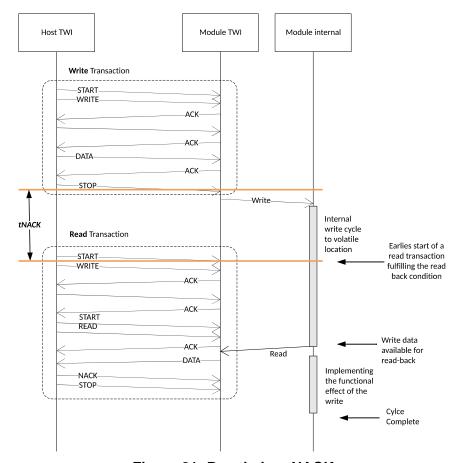

| 6  | Figure 21: Bus timing tNACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

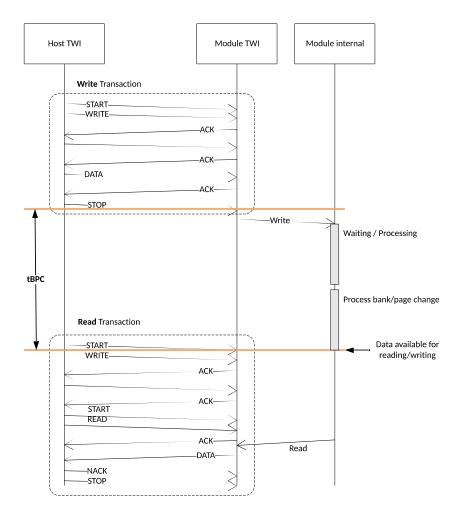

| 7  | Figure 22: Bus timing tBPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

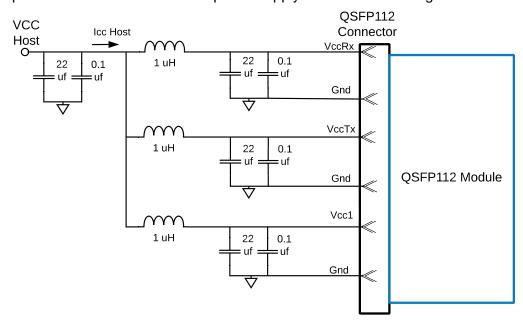

| 8  | Figure 23: Reference Power Supply Filter for Module Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 9  | Figure 24: Instantaneous and sustained peak currents for Icc Host (see Table 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

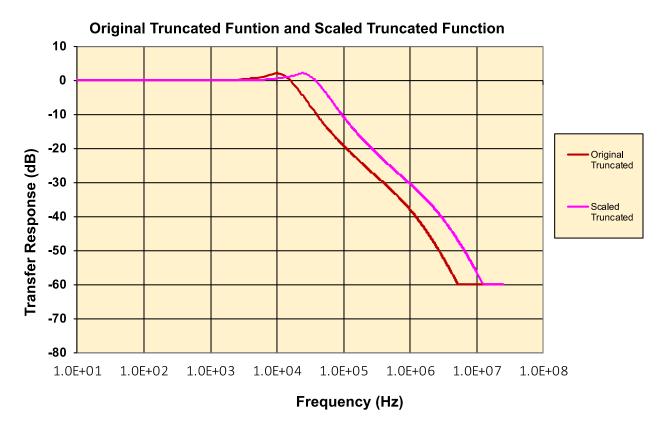

| 10 | Figure 25: Truncated Transfer Response for Host Board Power Supply Noise Output measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

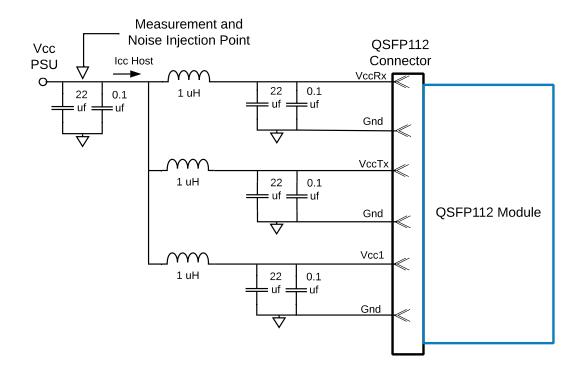

|    | Figure 26: Module Noise Injection Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 11 | Figure 27: Optical Media Dependent Interface port assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 12 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

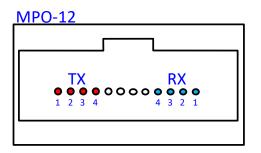

| 13 | Figure 28: MPO-12 One row optical patchcord and module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

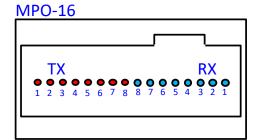

| 14 | Figure 29: MPO-16 One row optical patchcord and module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

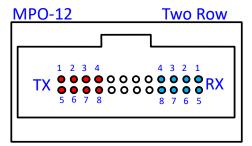

| 15 | Figure 30: MPO-12 Two row optical patchcord and module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 16 | Figure 31: Duplex LC optical patchcord and module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

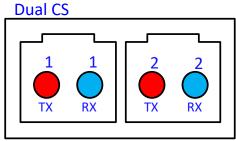

| 17 | Figure 32: Dual CS connector optical patchcord and module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

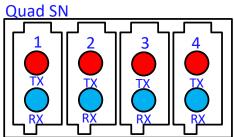

| 18 | Figure 33: Quad SN optical connector pathcord and four-port module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 19 | Figure 34: Quad MDC optical connector patchcord and four-port module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 20 | Figure 35: Dual SN optical connector patchcord and dual-port module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 21 | Figure 36: Dual MDC optical connector patchcord and dual-port module receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |